TFA - Transparent Live Code Offloading on FPGA

Utiliser des FPGA dans le design de dispositifs de calcul afin de pouvoir contourner les limitations physiques et technologiques est un phénomène qui a rapidement gagné de la popularité.

Néanmoins, même si cette évolution technologique permet d'ajouter des fonctionnalités avancées aux produits d'une façon compacte et rentable, la complexité globale du système est considérablement augmentée: profiter de ces nouvelles capacités demande en fait un large éventail de compétences qui sont rarement possédées par les entreprises et les institutions qui en ont besoin.

En raison de l'effort considérable exigé au moment du développement, l'applicabilité est souvent limitée à un groupe réduit de marques / modèles, tout en n'étant efficace que lorsque les cas d'utilisations prévus correspondent à l'utilisation réelle.

La synthèse de haut niveau (HLS) mitige partiellement ces problèmes en supprimant la barrière représentée par le langage de programmation. Cependant, la compilation et le déploiement d'un bit-stream est un processus extrêmement long.

De plus, le développement HLS étant aussi basé sur des cas d'utilisation, il pourrait résulter dans la sous-utilisation des ressources hardware.

Le projet TFA [1], développé par l'Institut REDS, suit la même philosophie des projets VPE [2] et HPA [3]: s'adapter dynamiquement aux données et aux ressources informatiques disponibles, tout en étant transparent au développeur.

La solution que nous proposons ne nécessite en effet aucune modification du code de l'application --- pas même des indications pragma pour guider l'optimisateur (bien que nous puissions bénéficier de leur présence) --- soulageant le développeur de la charge de connaître les détails de la plate-forme cible. De plus, elle n'a pas à prévoir les cas d'utilisation pour éviter les goulets d'étranglement de performance, et elle n'a pas non plus à décider de manière statique quelles parties du système doivent être accélérées: le système identifie de façon transparente les fragments de code susceptibles d'être parallélisés et il les envoie à la carte FPGA pré-programmée avec une sous-couche (une version améliorée de la sous-couche présentée dans Capalija et al., 2013). Comme le bit-stream que nous utilisons est fixe, et contrairement à HLS, nous pouvons modifier les fonctionnalités offertes par FPGA

à la volée, pour les adapter aux demandes d'utilisation actuelles. Enfin, puisque nous opérons au niveau de la Représentation Intermédiaire (IR) de LLVM, notre approche est agnostique du langage.

Comment fonctionne TFA ?

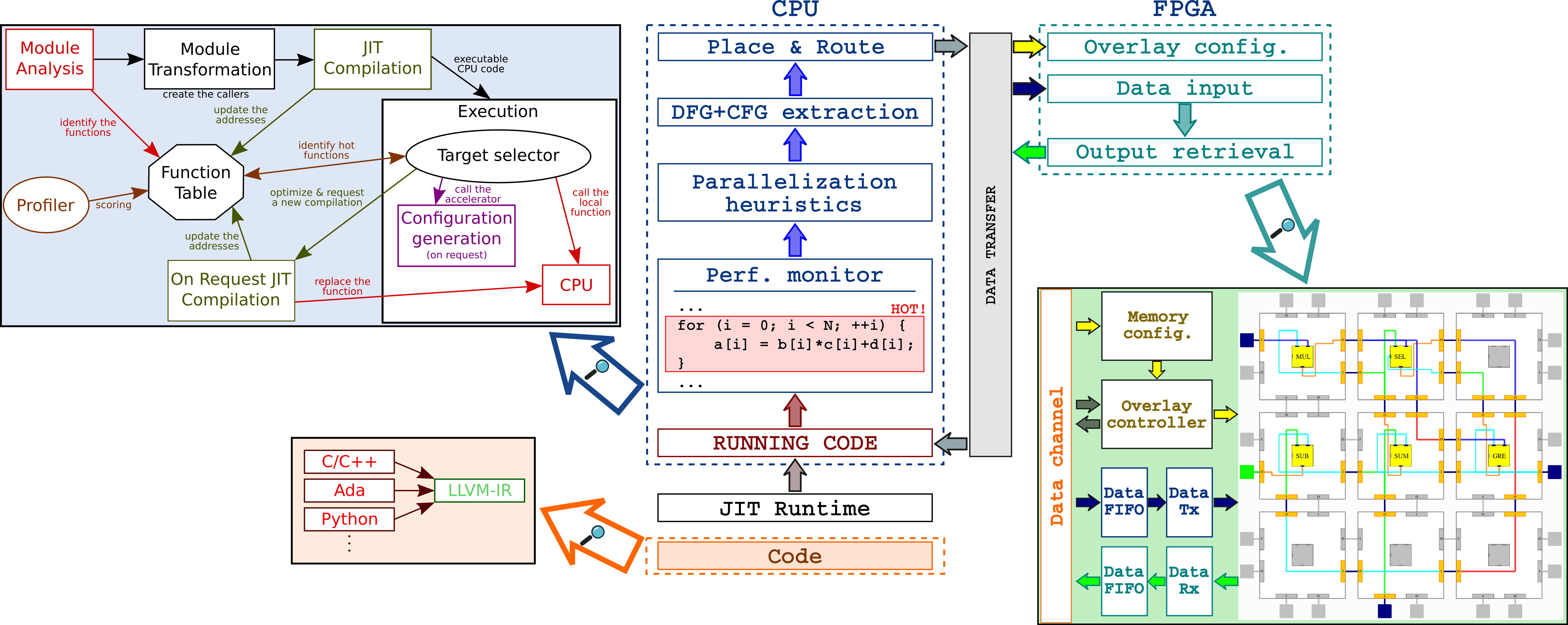

La figure 1 présente les principales composantes du système TFA. Un compilateur Just-In-Time (JIT), couplé à un moniteur de performances à bas débit, détecte automatiquement les fragments de code qui requièrent la plus grande fraction de ressources (temps d'exécution ou accès à la mémoire, par exemple). L'utilisation d'un cadre JIT est la clé de notre approche. En plus d'être capable d'effectuer des optimisations qui ne peuvent être appliquées qu'au moment de l'exécution, nous pouvons détecter quelles parties du code prennent la plus grande fraction de ressources en fonction des entrées courantes. Grâce à cette information, nous pouvons éviter de décharger des fragments de code sans importance qui entraîneraient peu de gain, tout en conservant le pouvoir de revenir sur ces décisions si ces fragments deviennent plus pertinents.

Une fois qu'une région de code est identifiée comme critique, elle est analysée pour exposer les opportunités de parallélisation. Le diagramme de flux de contrôle (CFG) et le graphique de flux de données (DFG) sont ensuite extraits et utilisés pour piloter le placement et le routage des unités fonctionnelles sur la superposition, qui sera appelé DataFlow Engine (DFE) ci-dessous. Enfin, la superposition FPGA est reconfigurée à la volée pour exécuter le nouveau modèle de flux de données. Une fois que cela est fait (cela nécessite quelques centaines de microsecondes), nous modifions le flux d'exécution du code comme dans HPA et alimentons le FPGA des données fournies par l'application en cours d'exécution. Une caractéristique importante de notre proposition est que nous ne sommes pas liés à une solution matérielle spécifique. Nous soutenons tous les FPGA et le DFE que nous avons adopté à une taille paramétrique pour s'adapter aux ressources disponibles des différents dispositifs. En outre, le revêtement choisi est juste un choix de commodité, comme notre architecture cadre est générique.

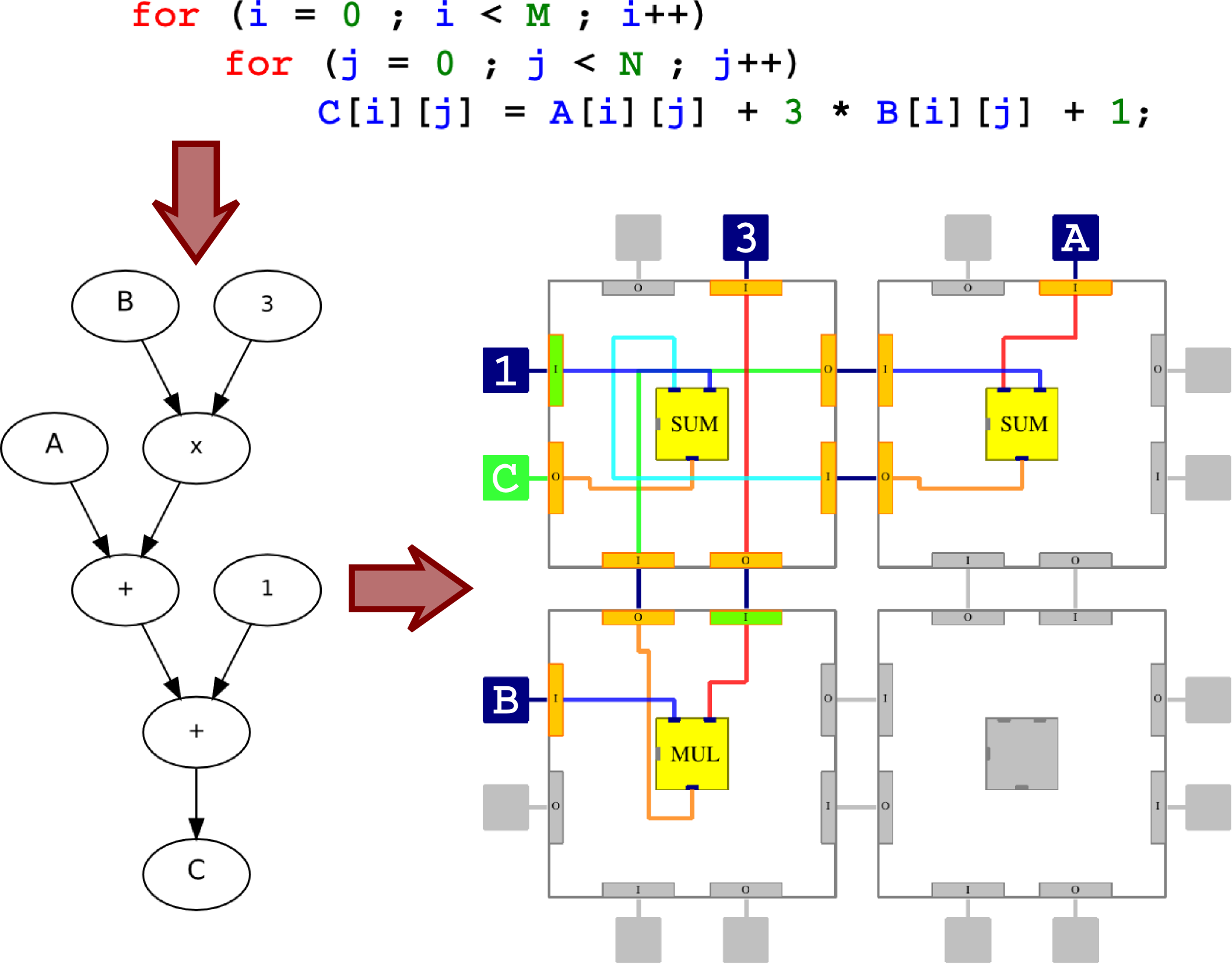

Un exemple d'exécution de TFA est montré dans la Figure 2: un fragment de code est d'abord converti dans le graphe correspondant, ensuite à 2x2 sous-couche est configurée pour exécuter les opérations demandées.

Puisque le mappage d'un graphe sur une sous-couche est un problème très complexe (encore pas résolu dans la littérature), nous utilisons un algorithme personnalisé de type Las-Vegas qui peut router efficacement plusieurs dizaines de nœuds.

Perspectives

Notre vision à long terme est de développer un framework qui réduit considérablement le temps de développement en permettant au code d'être écrit une seule fois, sous une forme plus naturelle pour le développeur de haut niveau, puis optimisé à la volée uniquement quand cela est nécessaire et selon les ressources matérielles disponibles. Ce serait une amélioration considérable par rapport aux techniques actuelles de HLS et faciliterait considérablement la transition vers des systèmes de calcul plus hétérogènes et beaucoup moins exigeants en énergie.

TFA @FPL2016

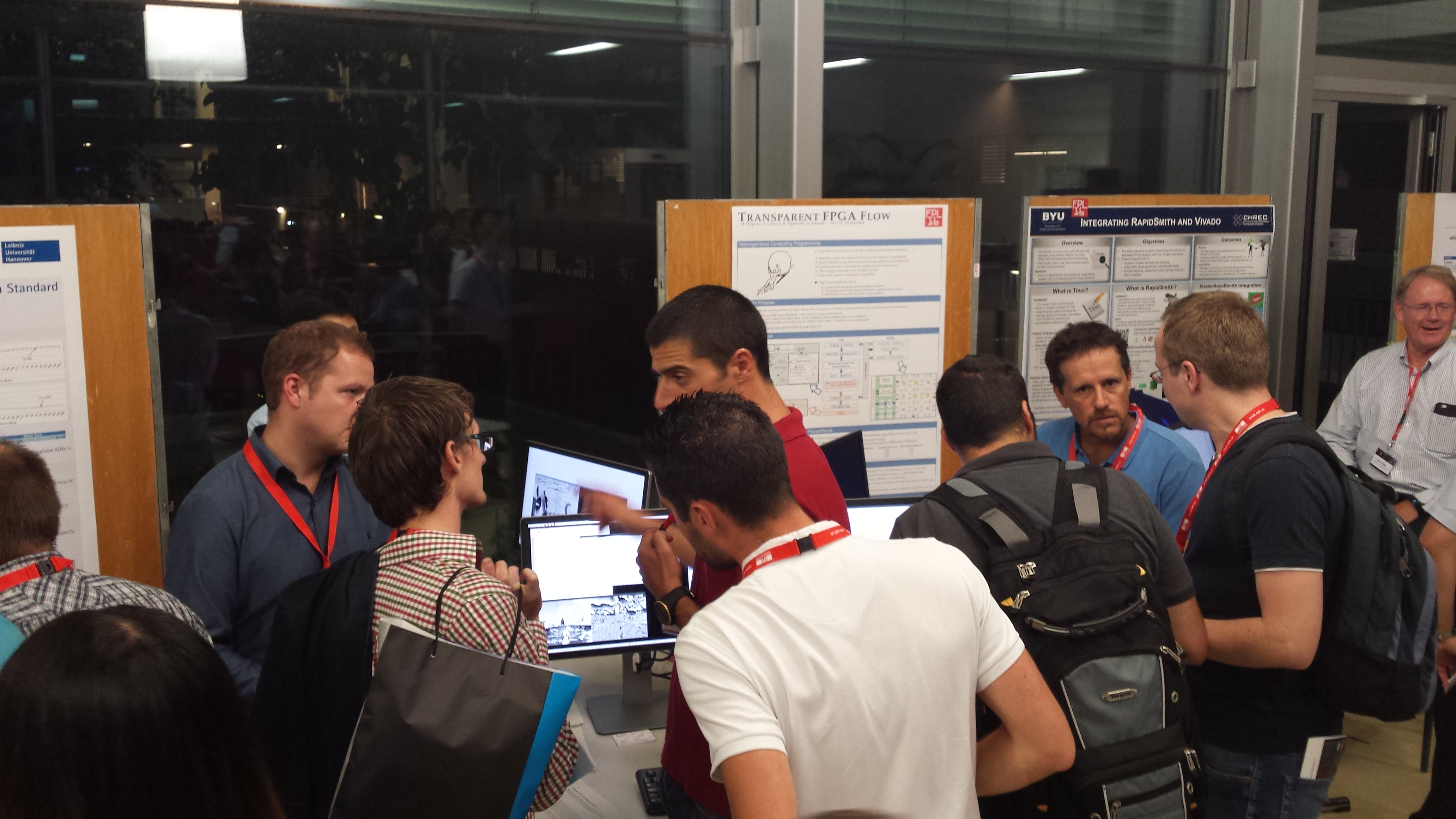

Nous avons présenté une démonstration de notre travail à la conférence FPL2016, recevant un feed-back très positif et des commentaires encourageants!

Publications

[1] R. Rigamonti, B. Delporte, A. Convers, A. Dassatti, “

Transparent Live Code Offloading on FPGA” - FSP 2016.

[2] B. Delporte, R. Rigamonti, A. Dassatti, “

Toward Transparent Heterogeneous Systems” - MULTIPROG 2016.

[3] B. Delporte, R. Rigamonti, A. Dassatti, “

HPA: An Opportunistic Approach to Embedded Energy Efficiency” - OPTIM 2016.