Présentation du projet Nano-Tera QCRYPT

A l'heure actuelle, une quantité extrêmement importante de données est échangée sur les réseaux informatiques. La cryptographie permet de réaliser ces échanges de manière sécurisée, sans qu'un tiers ne puisse mettre la main sur des données sensibles. Le concept est composé de deux parties: l'échange de clés, et le cryptage à l'aide de cette clé. Les systèmes actuels utilisent une clé réputée sure, mais qui pourrait souffrir de quelques faiblesses, notamment si l'ordinateur quantique venait à faire son apparition. Une réponse à cette faille est donnée par l'usage unique de la clé de cryptage. Bien que fournissant un cryptage totalement sûr, cette technique nécessite d'échanger une clé pour chaque communication, ce qui n'est pas possible à l'heure actuelle. En effet, la cryptographie quantique permet un échange de clé sûr, mais le débit ainsi atteint est nettement trop faible.

Ce projet vise donc à une très nette amélioration de la technologie actuelle. Premièrement, l'échange de clé basé sur les propriétés quantiques sera amélioré afin d'atteindre un débit de 1Mbps, très supérieur à ce qui est proposé actuellement. Deuxièmement, le cryptage sera également amélioré, et couplé à cet échange de clé. Les débits d'échange d'information cryptée devraient, durant ce projet, passer à 100Gb/s, alors qu'ils sont actuellement de l'ordre de quelques Gb/s. De plus, la transmission de données passera par les réseaux de fibre optique standards utilisés par les opérateurs de télécommunications, rendant possible leur déploiement à grande échelle.

Les retombées de ce projet, qui durera 3 ans, seront importantes pour plusieurs secteurs, et devraient pouvoir être exploitables de manière fiable. Les banques sont clairement intéressées par cette technologie, afin d'échanger de l'information sensible avec une sécurité largement supérieure à celle actuellement disponible. Les états sont également des utilisateurs potentiels, afin d'éviter que des informations sensibles ne tombent en des mains peu aimables. Enfin, à titre d'exemple, l'état de Genève a déjà utilisé un réseau de ce type dans le cadre des opérations de vote électronique, montrant un réel intérêt pour la cryptographie quantique.

Le consortium du projet est constitué par quatre équipes, soit le GAP de l’UniGe, l’IIS de l'ETHZ, trois instituts de la HES-SO (IICT, INIT, REDS) et un partenaire industriel IdQuantique SA. Le budget du projet est d'un peu plus de 4 millions de francs répartis sur trois années (2010-2013), dont 870kF seront reçus par la HES-SO (3/4 pour la HEIG-VD et un quart pour l'Hepia).

L'ensemble des professeurs de la HES-SO sont sous la direction d'Etienne Messerli de l'institut REDS de la HEIG-VD. L'équipe HES-SO est composée de trois instituts, soit INIT de l'hepia, l'IICT et le REDS pour la HEIG-VD. Voici la liste des professeurs par institut participant à ce projet:

- Fabien Vannel, INIT de l'hepia

- Juergen Ehrensberger et Pascal Junod, IICT de la HEIG-VD

- Etienne Messerli, Yann Thoma et Olivier Auberson (adjoint scientifique), REDS de la HEIG-VD

Le projet est décomposé en deux parties distinctes. La figure ci-dessous donne la décomposition du projet:

La figure montre un lien utilisant deux équipements symétrique afin de pouvoir transférer des données cryptée de façon sûr avec un débit de 0.1 TeraBps.

Le module QKD Engine (Quantum Key Distribution) doit permettre de générer des clés quantiques avec un débit de 1Mbps. La technologie est développée par l'équipe du GAP de l'université de Genève. Il s'agit de pouvoir utiliser une seule fibre et d'augmenter le nombre de clés générées. La réalisation de la plateforme embarqué est elle assurée par l'équipe de Genève et d'Yverdon-les-Bains. A noter que l'étude de concept de sécurité sont défini par Pascal Junod qui est un spécialiste de la sécurité et de la cryptographie.

Le module Encryption Engine doit permettre d'assurer le cryptage des données avec un débit de 100 Gbs à l'aide des clés fournies par le QKD. L'équipe de IIS de l'ETHZ développe une architecture de l'algorithme de cryptage AES pouvant fonctionner à 100GigaBps. Les équipes IIS et REDS ont collaboré afin de concevoir et développé une carte prototype permettant de connecter 10 liens à 10Giga et deux liens à 100Giga afin de pouvoir réaliser une première version de la liaison sécurisée à 100Giga. La mise en œuvre de cette carte est en cours actuellement.

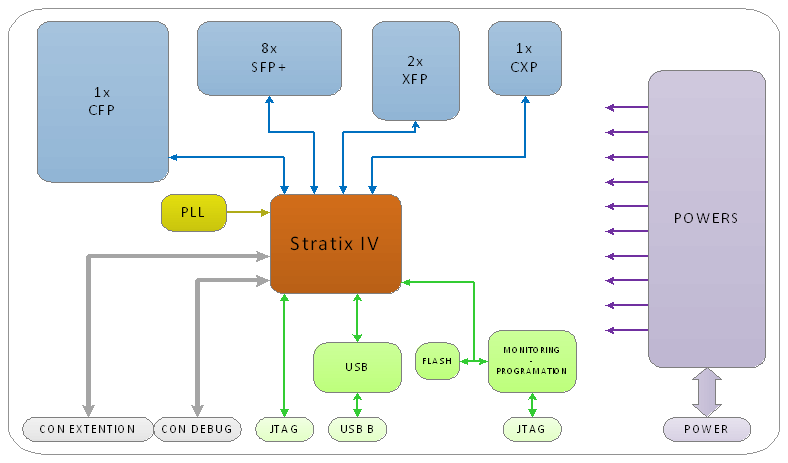

La carte prototype, illustrée sur la figure ci-dessous, a été développée conjointement entre le REDS, l'IIS et IdQ. Elle a pour objectif d'acquérir les compétences liées aux connexions haute vitesse réalisées sur PCB et contrôlées via un circuit logique programmable (FPGA) de dernière génération.

L'élément central de la carte est composé par la FPGA Altera Stratix IV GT (EP4S100G5 avec un boitier de 1932 pins). Elle comporte 32 liens 10Gb/s sur lesquels ont été connecté les transceivers optiques suivants :

- 8 SFP/SFP+ de 1G à 10G.

- 2 XFP à 10G.

- 1 CFP et 1 CXP pour les connections 40G et 100G.

L'ensemble des contraintes de la carte prototype, plus particulièrement la FPGA Stratix IV GT, les nombreux liens série, et les multiples alimentations ont nécessité un PCB de 24 couches. Ceci a permis de garantir la qualité de propagation et d'impédance des liaisons 10Gb/s, ainsi que la diffusion stable des tensions sur tous les composants.

L'ensemble des layer est réalisé sur la base de polymère FR-4 Nelco, offrant une bonne stabilité diélectrique pour les hautes fréquences. Le respect des caractéristiques électriques des liens à haute vitesse à nécessité l'utilisation de divers techniques. Nous avons ajouté des layers (GND) afin de garantir une l'impédance constante pour les paires différentielles. De même, les trous métallisés (via) des liens hautes vitesses ont été précisément dimensionnés et parfois repercés (backdrill) afin de supprimer toutes réflexions parasites.

Le bloc d'alimentation génère dix tensions différentes pour une puissance totale de 100 Watt. Leur contrôle est assuré par une CPLD MAX III permettant ainsi d'activer ou de désactiver chaque alimentation séparément. Ceci permet d'échelonner dans le temps le démarrage des circuits afin d'éviter un pic de consommation instantané. Un tel mécanisme devient nécessaire lorsqu'un composant telle la FPGA est capable de consommer jusqu'à 40W (40A @ 0V95) uniquement pour le fonctionnement de son cœur. Enfin, chaque tension est mesurée par un circuit spécifique qui transmet cette information à la CPLD permettant ainsi une gestion fiable des alimentations.

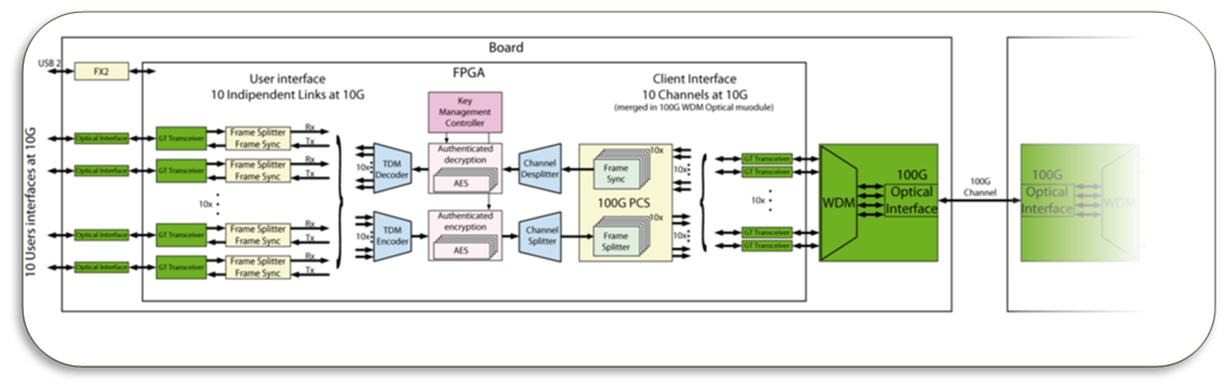

La FPGA, dont le diagramme des flux de données est représenté sur la figure ci-dessous, doit permettre de gérer les contraintes suivantes :

- Mise en œuvre des IP pour les transceivers Altera 10Gb/s.

- Contrôle des trames Ethernet à l'aide d'un bloc PCS.

- Répartition des flux de données au moyen de TDM.

- Encryption des données au moyen d'un bloc AES supportant un flux à 100Gb/s.

- Contrôle de la trame Ethernet avec un bloc PCS @100Gb/s et splitting sur dix liens 10Gb/s vers le module optique 100Gb/s.

Quelques points importants :

Ce design contient de multiples domaines d'horloges, notamment pour la gestion des transceivers (liens haute vitesse), le bloc PCS (décodage de la trame Ethernet) et le bloc AES. Il a donc été nécessaire d'introduire de nombreux FIFO pour faire le lien entre ces différents domaines.

Il a été également nécessaire de gérer les variations de fréquence du lien série 10Gb/s tant au niveau du jitter et que du drift entre les transceivers " émetteur " et " récepteur ". Une partie du travail est réalisé directement par les transceivers eux-mêmes (jitter). Le drift doit être compensé en introduisant, si nécessaire, des paquets " Idle " entre les trames Ethernet.

La conception d'un système aussi complexe implique l'utilisation de simulations efficaces. Celles-ci ont été réalisées à l'aide de bancs de test écrits avec le nouveau langage SystemVerilog. Celui-ci offre, entre autre, une programmation orientée objets, la génération de valeurs aléatoires, des transactions et des fonctions de couverture de test.

Toutes ces contraintes engendrent des problématiques complexes dans la FPGA. Il a été de ce fait nécessaire de réaliser le placement de certaines parties du design manuellement. Ceci est notamment vrai au niveau de la gestion des blocs utilisant des horloges à des fréquences supérieures à 200MHz, ainsi que pour le routage de bus conséquents (512bits).

Actuellement, la carte prototype a été mise en œuvre avec succès en septembre 2011. Un test utilisant trois transceivers mis en série a démontré le fonctionnement sans erreur d'une liaison utilisant des fréquences de 10GHz. Ensuite, il a été réalisé avec succès une communication 10Gb/s avec un équipement de test de génération et vérification de flux Ethernet. Ce second test a permis de valider le design FPGA gérant une liaison Ethernet à 10Gb/s. D'autre part le bloc de cryptage AES a été mis en œuvre avec succès sur un lien 10Gb/s.

L'étape suivante consiste à choisir un module optique 100Gb/s. Ce choix est extrêmement complexe par le nombre restreint de dispositif disponible sur le marché et leur prix très élevé de plusieurs dizaines de milliers de francs.

Ce projet prendra fin en mars 2013. Les premiers résultats obtenus nous rendent très confiant d'atteindre l'objectif du projet, soit une liaison à 100 Gb/s sécurisée.