Objectifs

Le projet EASY-PHI a pour but de fournir une plate-forme d'instrumentation scientifique "open hardware". Ce projet est réalisé dans le cadre du programme INTERREG. Le consortium du projet EASY‐PHI comprend différents acteurs de Haute‐Savoie (PLS, USMB/SYMME et MIND), du canton de Vaud (HEIG‐VD/REDS) et de Genève (IDQ et Unige‐GAP). Le consortium comprend ainsi des partenaires suisse et français.

Le secteur du logiciel a connu une formidable révolution avec l'apparition du modèle "open‐source" qui a permis à plusieurs acteurs d'émerger (comme par exemple Red Hat ou Mozilla). Au niveau matériel (Hardware) un mouvement comparable émerge; à l'heure actuelle différentes initiatives existent, nous pouvons cité par exemple Arduino, néanmoins c'est un modèle qui doit encore faire ses preuves et qui présente un fort potentiel de développement. Dans ce contexte, le projet EASY‐PHI a pour but de fournir une plate‐forme d'instrumentation scientifique "open‐hardware".

Actuellement, les équipements d'instrumentation scientifique sont volumineux, contraignants en terme d'utilisation, onéreux et chacun d'eux est dédié à une application spécifique. Usuellement chaque équipement d'instrumentation scientifique comprend une partie matériel spécifique qui n'est pas modifiable par l'utilisateur.L'approche EASY‐PHI permettrait de lever ces contraintes en proposant une plate‐forme d'instrumentation scientifique ouverte, modulaire, générique et collaborative. Il existe actuellement un prototype développé à l'Université de Genève (équipe du GAP ‐ http://www.easy‐phi.ch/) pour des applications d'optique quantique.

La plate‐forme est composée d'un châssis mécanique intégrant des cartes électroniques, chacune de ces cartes ayant une fonction définie (par exemple l'acquisition de données rapides). L'objectif de ce projet est de fournir un standard de base comprenant un protocole de communication, une carte de base (template), de procéder à son industrialisation et développer des produits associés afin d'étendre les cas d'utilisations à d'autres domaines scientifiques. Les travaux de définition des caractéristiques et spécificités de la plate‐forme seront réalisés en commun par tous les partenaires du consortium. Durant le projet, les parteniares vont contribuer à élargir les possibilités d'utilisation du rack par la réalisation d'une carte pour leur domaine d'activités.

Activités de l'institut REDS de la HEIG-VD

Dans le cadre de ce projet, l'institut REDS va partiper aux actions suivantes:

* Définition des spécifications du standard EASY‐PHI et création d'une association

* Réalisation de la carte de base pour le standard EASY-PHI (board template)

* Conception et réalisation d'une carte de développement SoC-FPGA

* Développement d'une application pour la carte SoC-FPGA

Standard et association EASY-PHI

Un standard sera définit dans le cadre du projet permettant de pouvoir intégrer différentes cartes dans el mêm rack. Ce standard spécifiera l'architecture du rack et les différentes possibilité de control et de configuration. Ce standard sera complété par une carte de base qui comprendra la partie commune à toutes les cartes pour leur intégration dans le dit rack.

Dans le but de soutenir la diffusion du standard après la fin du projet différents solutions sont prévues. Une association sera crée dans le but d'assurer le maintien et l'évolution du standard. La promotion du standard EASY‐PHI sera réalisée via un site internet, la réalisation de publications scientifiques et de présentation par les membres du consortium lors de conférences. En effet, le maintien du site web www.easy‐phi.ch permettra d'assurer une visibilité quant à l'évolution de la plate‐forme EASY‐PHI, des cartes électroniques existantes ou à venir et d'animer une communauté d'utilisateurs EASY‐PHI (via un forum et une plate‐forme collaborative).

Carte de base EASY-PHI

Cette phase du projet compred la réalisation d'une carte électronique de base fonctionnelle comprenant la partie générique commune aux cartes EASY‐PHI sans partie applicative spécifique. Le schéma et le routage de cette carte électronique seront mis à disposition des développeurs externes.

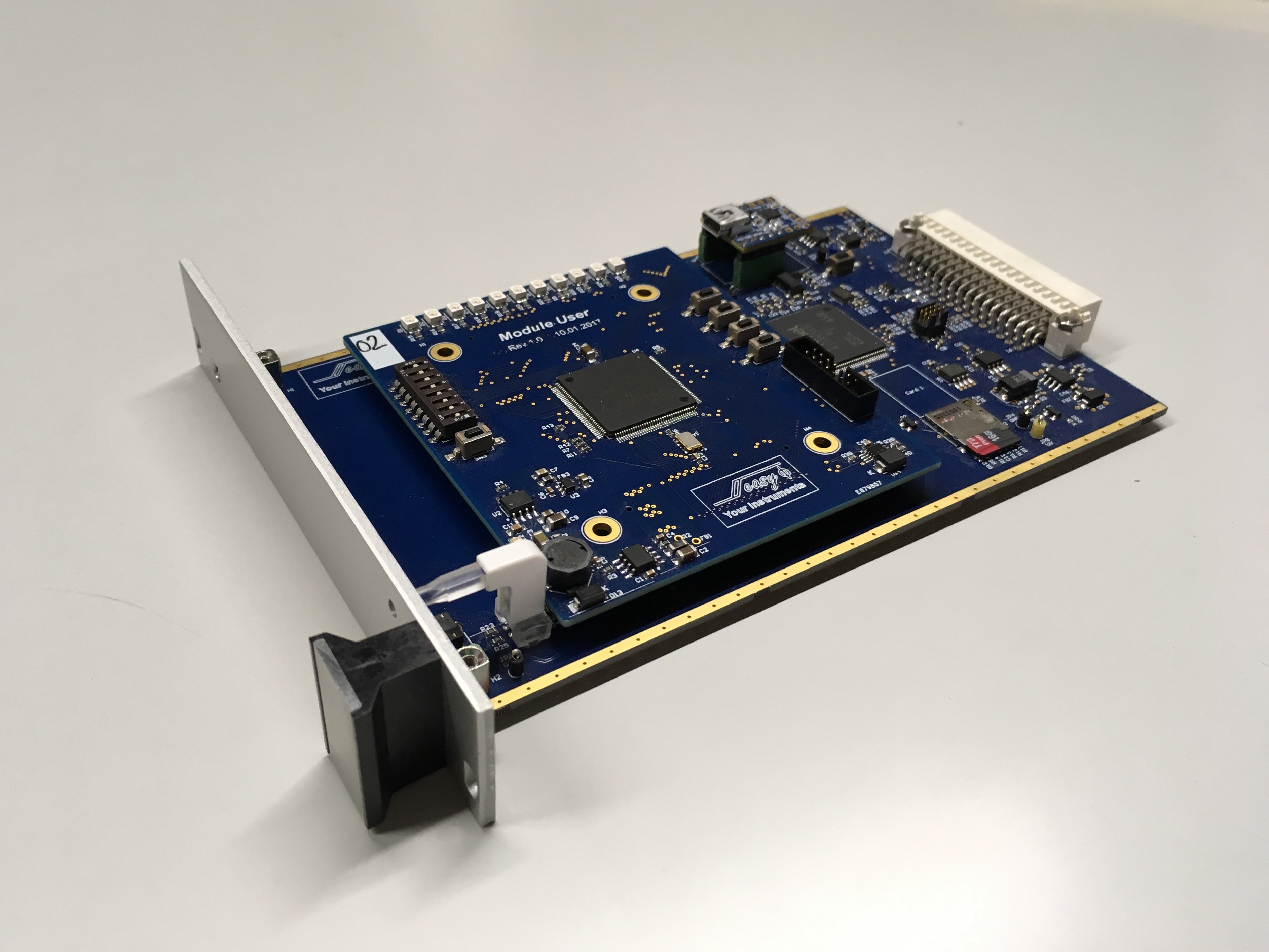

L'institut a réalisé cette carte en correspondance avec le standard définit avec les partenaires. Cette carte a été réaliser afin de permettre son montage à la main. Nous avons prévu de pouvoir implémenter une carte mezzanine pour que chacun puisse rapidement intégrer une partie spécifique. Un exemple de carte mezzanine a été réalisée avec une petite FPGA et des I/Os simple.

Cette étape a été terminée au début 2017. Voiic une vue de la carte template avec la carte mezzanine avec la FPGA Spartan 6.

Conception d'une carte de développement SoC-FPGA

L'objectif de cette action est de pouvoir disposer d'une carte de traitement à haute performance disposant d'un SoC-FPGA pour le rack EASY-PHI.

L’évolution de la technologie nous permet de disposer de nouveau circuit comprenant un double coeur ARM et une FPGA. Il est dès lors possible de réaliser des SoC (System on Chip) comportant une partie logicielle et une partie de logique programmable à l'aide d'un unique composant. La conception de tel système SoC implique la maitrise de nombreux aspects. Nous pouvons identifier les points suivants :

* réalisation d’un PCB complexe (densité, nombre de couches, lien à haut débit, etc)

* séquence de démarrage (boot) et portage d’un système d’exploitation (OS)

* communication entre partie software et hardware

* conception et vérification du design numérique de la FPGA

* validation et test de l’ensemble du système SoC

* mise en place d'un environnement de développement

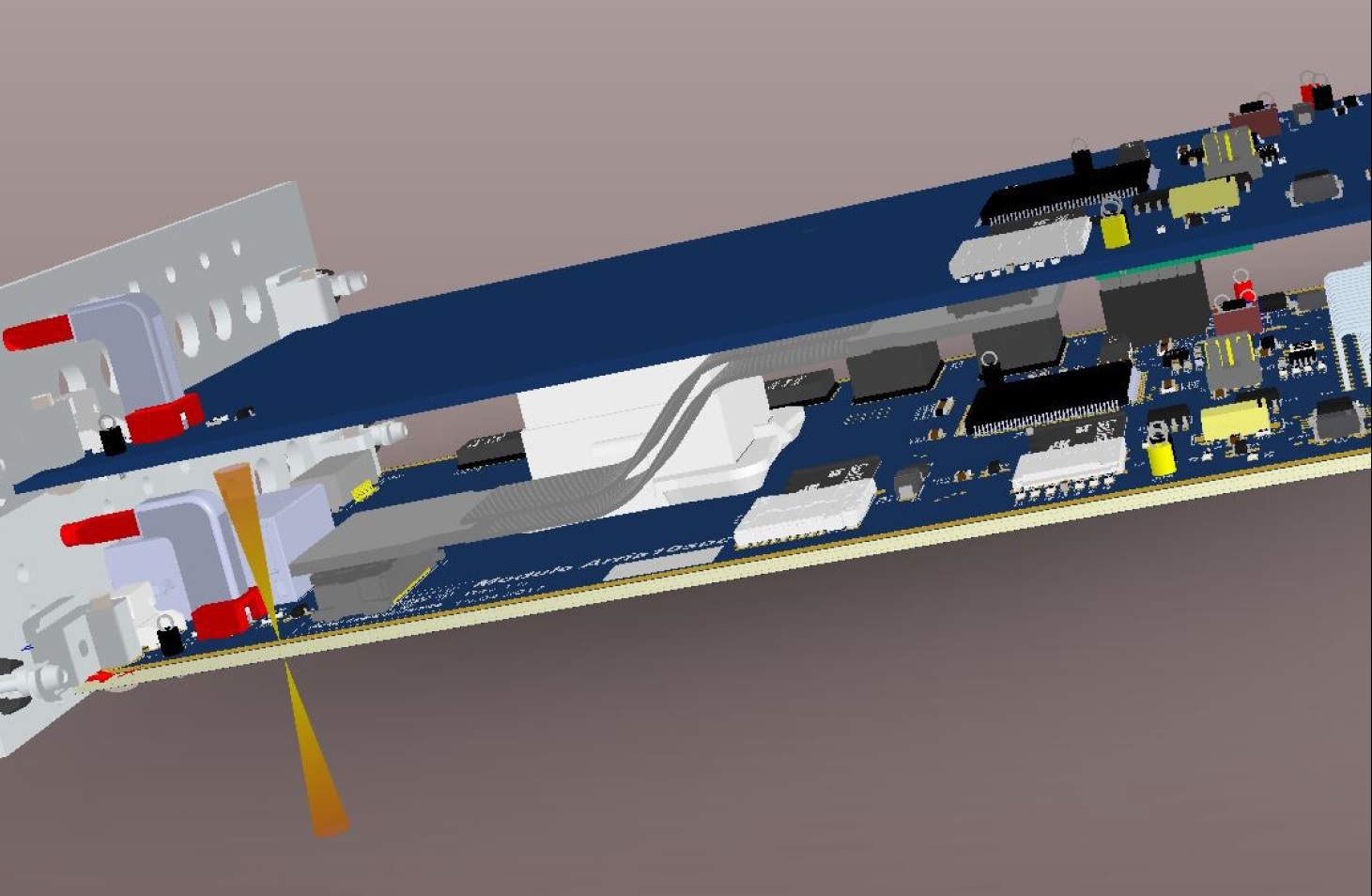

L’objectif est de concevoir une carte basé sur un SoC Arria 10 d'Intel disposant d'un connecteur d'extension. Voici une liste des spécifications de cette cartes:

* Altera Arria 10 SOC (SX 160), comprenant: 240 GPIO, 12 Transceivers 17.4Gbps, 160K LEs, Dual-core ARM Cortex A9

* mémoire de boot QSPI

* carte SD-card

* DDR3 2G Bytes

* Ethernet

* Entrées/sorties analogiques avec convertisseur rapide (150 à 200 Mega sample/sec)

* Liens série à haut débit 10giga/sec

* Entrées/sorties digitales

* Bus parallèle avec la partie générique communne EASY-PHI (uC Atmel)

La schématique de la carte a été terminée en été 2017. Nous avons démarré le routage de la carte. Voici une vue d'ensemble de la carte en 3D.

Développement d'une application pour la carte

SoC-FPGA

Afin de démontrer les performances de cette carte SoC-FPGa, il est prévu de l'utiliser pour une application. Nous sommes en cours d'évaluation de l'application la mieux adaptée pour cet objectif.