Dès lors, la réalisation de systèmes embarqués nécessite fréquemment l'utilisation d'une FPGA pour atteindre les performances souhaitées. Ce type de circuit permet de réaliser, de manière efficace, une partie du traitement à côté du processeur. Il s'agit donc de mettre en œuvre des solutions de Co-design. L'architecture classique des systèmes à processeur ne permet pas d'utiliser efficacement les performances délivrées par une FPGA.

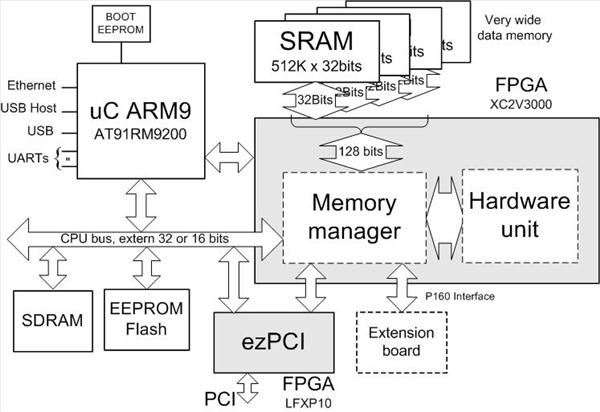

Microcontrôleur ARM 9:

Le microcontrôleur est utilisé pour configurer et gérer les différents périphériques de la carte. Il gère notamment les liaisons USB, Ethernet et l'UART. Il dispose d'une mémoire Flash 16 bits, d'une SDRAM et d'une EEPROM. La mémoire Flash contient le bootloader (U-Boot) ainsi que le noyau compressé. Une fois que le bootloader a terminé la configuration du ARM le noyau ce décompresse en SDRAM. Nous disposons actuellement d'une version de Boot avec LINUX 2.6.20.

FPGA Lattice:

La LFXP10 est principalement dédiée à la gestion de la communication vers un PC via PCI. Les IP suivantes peuvent y être implémentées : PCI-33MHz, PCI 66MHz, PCI-X 133MHz. Toutes ces IP ont été développées par l'institut REDS. Nous avons également réalisé une IP PCI express qui serra utilisée lors de la prochaine "Release" de la carte. Les informations envoyées par le PC sont redirigées soit vers le microcontrôleur soit vers la FPGA Xilinx.

FPGA Xilinx:

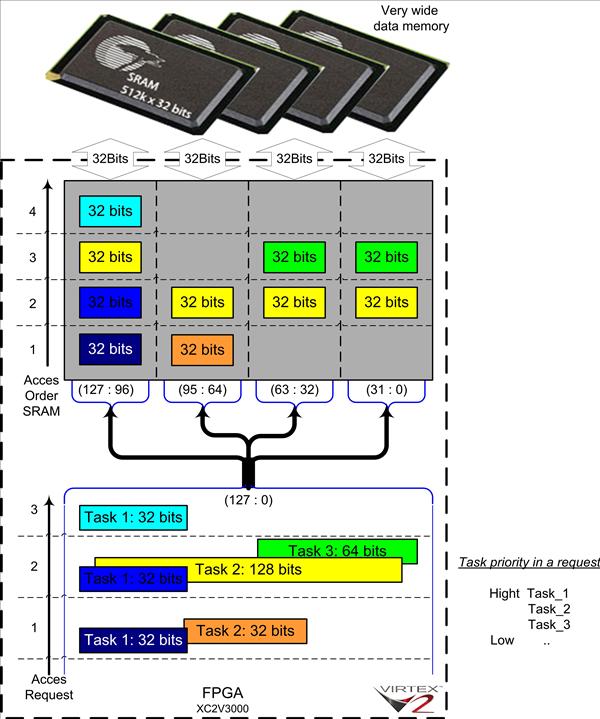

La XC2V3000 est utilisée comme co-processor. Elle gère les différentes "Taches" qui lui sont dédiées, comme par exemples un cryptage AES, un traitement d'images ou un traitement vidéo.

La FPGA intègre un manager permettant de gérer les différentes "Taches" ainsi que les différents accès de celles-ci vers la SRAM. La gestion des accès permet aux différentes "Taches" d'accéder régulièrement à la SRAM, ceci afin d'éviter que la SRAM ne soit monopolisée que par une seule "Tache".

Perspectives

Validation de la plateforme de test pour le transfert de données à haut débit. Celle-ci intégrera un algorithme de cryptage AES dans la Xilinx. En collaboration avec le HUG de Genève, la carte va être utilisée pour le traitement d'images fournies par un IRM. Les données seront fournies via la ligne Ethernet. La FPGA servira aux différents traitements de l'image. Les résultats seront ensuite redirigés vers le PC via le port PCI.