Haute Ecole d'Ingénierie et de Gestion du Canton de Vaud

# Electronique Numérique 4ème tome

Systèmes séquentiels avancés MSS complexes

Etienne Messerli Sylvain Krieg Mars 2013 Version 0.4b

## Mise à jour de ce manuel

Je remercie tous les utilisateurs de ce manuel de m'indiquer les erreurs qu'il comporte. De même, si des informations semblent manquer ou sont incomplètes, elles peuvent m'être transmises, cela permettra une mise à jour régulière de ce manuel.

Etienne Messerli

#### Contact

Auteurs: Etienne Messerli Sylvain Krieg

e-mail : etienne.messerli@heig-vd.ch Tél: +41 (0)24 / 55 76 302 -

#### Coordonnées à la HEIG-VD :

Institut REDS HEIG-VD Haute Ecole d'Ingénierie et de Gestion du Canton de Vaud Route de Cheseaux 1

CH-1400 Yverdon-les-Bains Tél: +41 (0)24 / 55 76 330 Internet: http://www.heig-vd.ch

Institut REDS

Internet: http://www.reds.ch

Autres personnes à contacter:

M. Gilles Curchod gilles.curchod@heig-vd.ch Tél direct +41 (0)24/55 76 259

# **Table des matières**

| Chapi  | tre 1 Décomposition machine séquentielle comp        | olexe 1 |

|--------|------------------------------------------------------|---------|

|        | Structures des unités de commande                    |         |

|        | Structure de l'unité de traitement                   |         |

|        | Combination act structures a CC et a C1              |         |

| Chapi  | tre 2 Méthode de conception                          | 13      |

| -      | tre 3 Application de la méthodologie de conception   | àla     |

| multip | olication                                            | 17      |

| 3-1    | . Spécification de la multiplication séquentielle    | 17      |

|        | Schéma-bloc général                                  |         |

| 3-2    | 2. Algorithme : organigramme ou graphe               | 19      |

| 3-3    | 3. Partition unité de commande / unité de traitement |         |

|        | Identification des fonctionnalités de l'UT           |         |

|        | Unité de traitment                                   |         |

| 3-4    | L. Passage d'un organigramme à un graphe             | 28      |

|        | Remarque importante                                  |         |

| 3-5    | 5. Organigramme détaillé                             | 32      |

| 3-6    | 5. UC câblée                                         |         |

|        | Decription VHDL de l'UC câblée                       |         |

| 3-7    | . Exercices                                          | 39      |

| Chapi  | tre 4 Exemple :Distributeur automatique de billets   | 41      |

| I'-    | Introduction                                         |         |

| 4-1    | Spécifications du distributeur                       |         |

|         | Fonctionnement désiré                        | 42  |

|---------|----------------------------------------------|-----|

|         | Collecteur de monnaie                        | 42  |

|         | Échangeur de monnaie                         | 44  |

|         | Description des signaux                      | 44  |

|         | Mécanisme distributeur de billets            | 45  |

| 4-2.    | Schéma-bloc général et organigramme grossier | 46  |

| 4-3.    | Partition commande / traitement              | 48  |

| 4-4.    | Exercices                                    | 51  |

| 4-5.    | Organigramme détaillé                        | 52  |

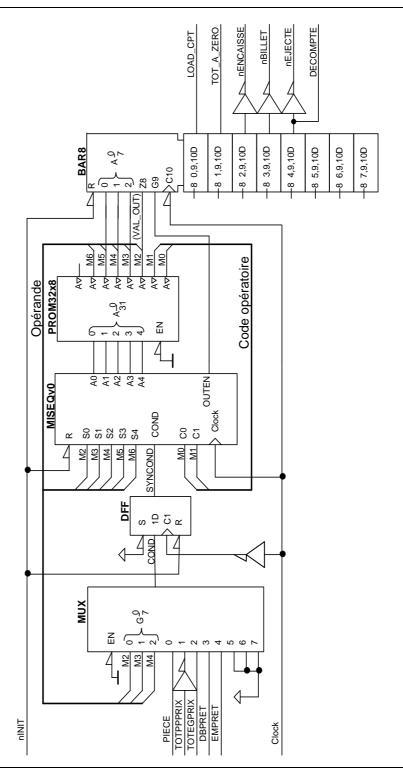

| 4-6.    | UC câblée                                    | 57  |

|         | Description VHDL de l'UC câblée              | 59  |

| 4-7.    | Exercices                                    | 61  |

|         |                                              |     |

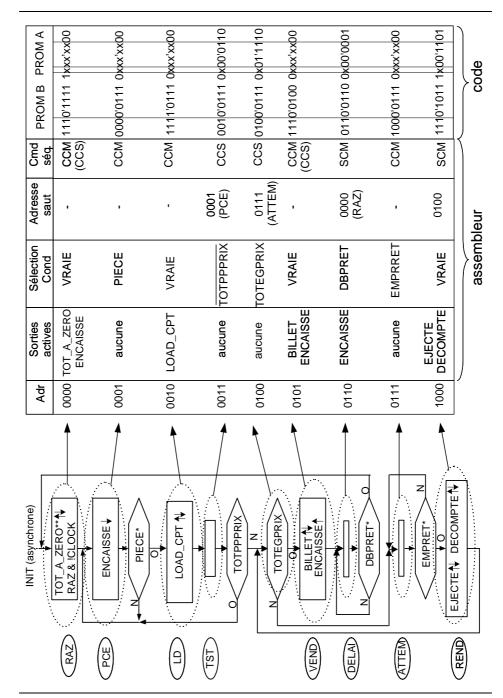

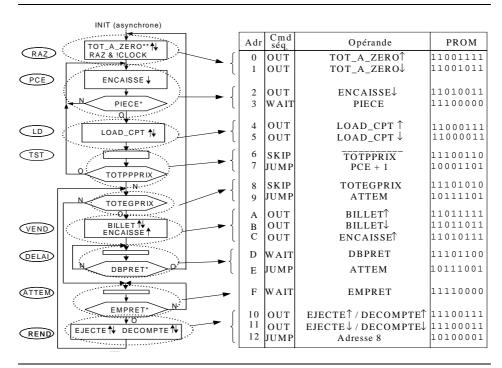

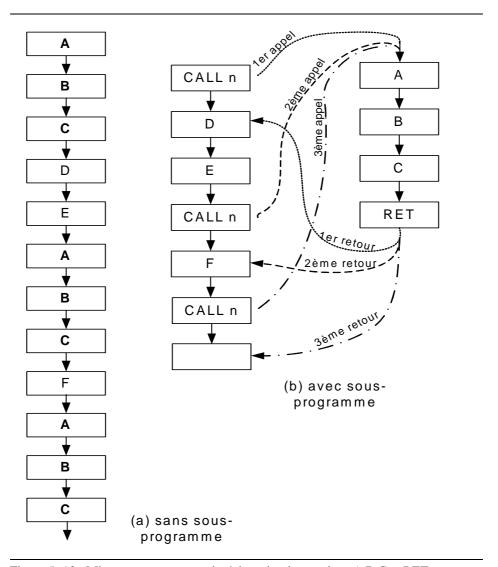

| Chapit  | re 5 Unité de commande microprogrammée       | 63  |

| 5-1.    | Exercices                                    | 71  |

| 5-2.    | Minimisation de la mémoire de microprogramme | 72  |

| 5-3.    | Codage des sorties                           | 76  |

| 5-4.    | Exercices                                    | 78  |

| 5-5.    | Sous-programmes et interruptions             | 80  |

| Chapit  | re 6 Unité de traitement universelle         | 85  |

| -       | raphie 97                                    |     |

| 2101108 | Manuel de la HEIG-VD                         | 0.7 |

|         |                                              |     |

|         | Médiagraphie                                 |     |

## Chapitre 1

# Décomposition machine séquentielle complexe

La méthode de conception d'une MSS que nous avons étudiée au chapitre MSS simple, basée sur la description du comportement désiré à l'aide d'un graphe d'états, ne permet pas de s'attaquer à des MSS complexes. À partir de quelques dizaines d'états et trois ou quatre entrées, le graphe devient en effet fort malaisé à établir, la recherche d'un codage efficace devient un vrai casse-tête et le test devient un problème majeur.

Lorsqu'un problème devient trop volumineux pour être étudié et résolu globalement, la stratégie qui a fait ses preuves dans toutes sortes de domaines consiste à découper progressivement ce gros problème en problèmes partiels, plus petits et plus faciles à résoudre, jusqu'à ce que chaque problème partiel puisse être traité sans trop de difficulté avec les moyens à disposition. Nous chercherons donc à découper les machines séquentielles complexes, c'est-à-dire comportant beaucoup d'entrées, de sorties et d'états, en plusieurs machines plus simples.

Il existe des approches théoriques visant au découpage d'une MSS complexe. Dans la pratique, elles n'ont que peu d'utilité car il faut généralement commencer par décrire la machine complète de façon détaillée, ce que nous voulons précisément éviter. De plus, elles ne favorisent pas l'identification des sous-machines déjà réalisées, ou pouvant être adaptées sans difficulté à partir de celles-ci, ce qui est précisément notre but. Comme exemple de sous-machines existantes, nous pouvons citer toutes celles composées d'une fonction standard, tel que compteur, registre à décalage, comparateurs, .. Ces sous-machines sont très facilement adaptables.

La décomposition d'une MSS, partie essentielle de la conception est au moins autant **un art qu'une science**. L'imagination et l'expérience du concepteur auront donc une influence prépondérante sur la qualité des solutions générées. Nous allons nous efforcer de développer l'une et l'autre par la pratique. Mais l'art est toujours tributaire de la technique, qui fera ici la différence entre le bricoleur et l'ingénieur. Nous allons donc acquérir les techniques nécessaires.

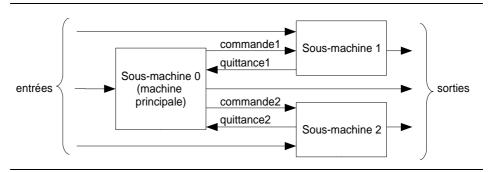

Parce que plus facile à concevoir et à réaliser, le découpage le plus utilisé est un découpage hiérarchique : une des sous-machines gère le fonctionnement des autres. La figure 1- 1 schématise une telle situation, avec un découpage en 3 parties d'une machine complexe : la sous-machine 0 commande les sous-machines 1 et 2 et peut être appelée machine principale (dans toute hiérarchie, celui qui commande se croit plus important que les autres).

Figure 1-1: Découpage en sous-machines

Chaque flèche dans la figure 1- 1 doit-être vue comme pouvant représenter plusieurs signaux.

Le découpage hiérarchique ne s'arrête pas forcément à deux seuls niveaux hiérarchiques. Si la sous-machine 1 de l'exemple ci-dessus reste trop complexe pour être conçue d'un bloc, rien ne nous empêche de la décomposer à son tour en une sous-sous-machine principale et d'autres sous-sous-machines commandées par cette dernière. Et ainsi de suite. Mais deux niveaux hiérarchiques suffisent dans beaucoup de cas, et ils suffisent certainement pour étudier les notions de base qui font l'objet de ce cours. Dans ce qui suit, nous nous restreindrons donc à deux niveaux.

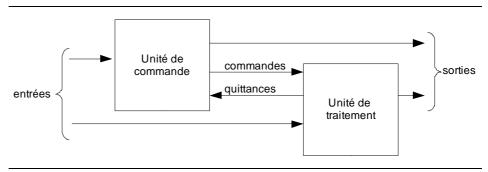

La différenciation du rôle joué par la machine principale d'une part et les autres sous-machines d'autre part, est un point essentiel de la méthode que nous allons développer. La machine principale est appelée unité de commande ou encore unité de séquencement, ou plus simplement séquenceur (System Controller, Control Unit ou Sequencer, en anglais). Les autres sous-machines sont regroupées sous le nom d'unité de traitement, ou unité d'exécution (Execution Unit ou Data Unit, en anglais). Il en résulte le schéma-bloc général de la figure 1- 2.

Figure 1-2: Séparation UC/UT

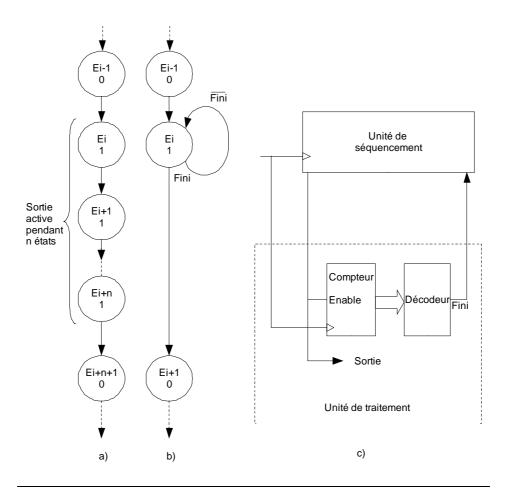

Un autre point essentiel de la méthode de synthèse des machines séquentielles complexes est qu'au lieu de voir le fonctionnement d'une MSS complexe comme une succession d'états décrite à l'aide d'un graphe, nous le verrons comme une suite d'opérations réalisées par l'unité de traitement et commandées, dans la séquence voulue, par l'unité de commande. L'avantage réside dans le fait que la suite d'opérations sera beaucoup plus petite que la suite d'états de la MSS. Prenons un exemple : envisageons une MSS qui doit, à un certain point de son fonctionnement, activer une sortie pendant n périodes d'horloge avant de continuer sa séquence. En suivant les méthodes du chapitre précédent, nous introduisons n états dans le graphe, qui serviraient à compter les périodes d'horloge, selon la figure 1-3 (a). Mais en délégant la tâche de compter les n périodes d'horloge à un compteur faisant partie de l'unité de traitement, comme nous le montre la figure 1-3 (c), le graphe de l'unité de commande (qui est aussi une MSS) ne comportera qu'un seul état pour activer cette sortie. La figure 1-3 (b) nous montre cette décomposition.

Figure 1-3: Traitement du comptage par l'UT

D'une façon générale, l'unité de commande d'une MSS complexe comportera beaucoup moins d'états que n'en aurait comporté la même machine conçue d'un seul bloc selon les méthodes du chapitre précédent (à supposer que nous soyons capables de concevoir cette machine). Par contre une machine conçue en séparant séquencement et traitement va comporter plus de portes et de flip-flops qu'une machine conçue d'un seul bloc. En chiffrant l'exemple ci-dessus nous en obtenons facilement la preuve : pour un nombre total d'états de la MSS conçue d'un seul bloc égal à 75, dont 50 pour générer l'impulsion de sortie, nous aurions besoin d'au moins 5 flip-flops pour la MSS à 26 états mais le compteur comportera 6 flip-flops, ce qui fera un total de 11.

Si la décomposition d'une MSS à tendance à augmenter le nombre de portes et de flip-flops, elle permet par contre de mieux tenir compte des composants existants et donne lieu facilement à des réalisations plus compactes dès qu'un certain seuil de complexité est dépassé. Ce seuil varie bien sûr avec l'apparition de nouveaux circuits et de nouvelles méthodes. Mais dans tous les cas, la décomposition d'une MSS complexe permet de diminuer très sensiblement le coût et la durée de son développement (conception + réalisation + tests), ainsi que les risques d'échec. Une bonne partie de ces gains viennent du fait que l'unité de traitement sera essentiellement

composée de fonctions standard, il est ainsi possible de réutiliser des éléments pour l'unité de traitement. Il faut entendre par "fonctions standard", des fonctions combinatoires ou séquentielles d'usage courant telles que le multiplexage, le décodage, la comparaison, le comptage ou le décalage. Pour ces fonctions il est possible de réutiliser des descriptions VHDL, ou d'utiliser des librairies dans les logiciels EDA où il existe des circuits intégrés spécifiques standard. Il n'est donc pas nécessaire de développer ces fonctions à chaque nouveau projet, mais il suffit de les adapter à nos besoins.

#### Structures des unités de commande

Bien qu'elle effectue elle-même parfois une partie du traitement de l'information, l'unité de commande a pour rôle principal de générer la séquence de commandes gérant le fonctionnement de l'unité de traitement. L'unité de commande, que nous abrégerons désormais UC, est donc une machine séquentielle appelée à générer une séquence de commandes. Ces commandes sont souvent appelées "instructions", et la séquence est aussi appelée "programme".

Les UC peuvent être séparées en deux types : les UC câblées et les UC microprogrammées. Cette distinction est justifiée par des différences importantes au niveau de la structure, la méthode de conception, les performances et les domaines d'application.

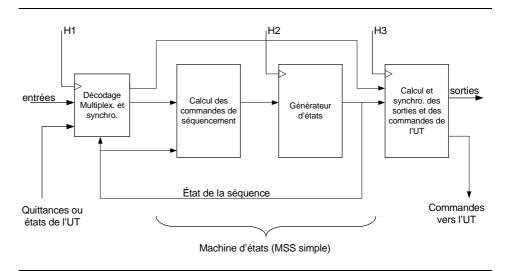

Une UC est dite "câblée" lorsque tout changement de son comportement nécessite un changement de son "câblage", soit des interconnexions entre les circuits qui la composent. Son schéma-bloc général est celui de la figure 1-4.

Figure 1-4: Schéma bloc général d'une UC câblée

Ce schéma-bloc fait apparaître un découpage et une terminologie plus adaptée aux machines complexes.

Les entrées de l'UC sont des entrées de la machine complexe (pas forcément toutes, certaines peuvent agir directement sur l'unité de traitement) et des quittances ou états provenant de l'unité de traitement, ci-après abrégée UT (voir figure 1-2). Un premier bloc va procéder aux décodage, multiplexage et synchronisation éventuellement nécessaires. Le décodage permet de séparer les informations en signaux distincts, plus faciles à utiliser que des codes mutli-bits. Le multiplexage permet de réduire le nombre apparent des entrées dans le bloc de calcul des commandes de séquencement. En effet, dans les machines complexes, il est rare que l'évolution depuis un état donné dépende de plus qu'une ou deux des très nombreuses entrées. Il est ainsi avantageux de multiplexer les entrées en fonction de l'état de la séquence.

Le bloc de calcul des commandes de séquencement n'est rien d'autre que ce que nous appelions le décodeur d'état futur. Le nouveau nom vient du fait que ce bloc ne calcul le code de l'état futur que dans le cas où il agit directement sur des flip-flops d'état de type D. En fait, comme le schémabloc l'indique, l'état de la séquence est généré par un bloc nommé "générateur d'états", qui peut en effet être simplement un ensemble de flip-flops, mais aussi un compteur, un registre à décalage ou une autre machine séquentielle. Ce que nous appelions un décodeur d'état futur génère donc des commandes qui vont provoquer la génération d'un nouvel état, plutôt que l'état futur lui-même.

Le dernier bloc calcule ( et éventuellement synchronise) les commandes de l'UT et des sorties de la machine (pas forcément toutes les sorties, certaines d'entre elles pouvant être générées par l'UT).

Avant l'apparition des PLDs, les UC câblées étaient réalisées à l'aide de circuits spécialisés standard (multiplexeurs, décodeurs, portes, flip-flops, compteurs et registres, essentiellement). Tout changement du câblage impliquait de couper des pistes sur le circuit imprimé et d'ajouter des fils soudés aux pattes des ICs, ou de refaire carrément la conception d'un circuit imprimé. Si un circuit intégré sécifique (ASIC = Application Spécific Integrated Circuit) avait été réalisé, tout changement de comportement (ou la correction d'une erreur) demandait une reconception impliquant des coûts et des délais importants.

Depuis l'apparition des PLDs, le câblage est en bonne partie programmable, ce qui augmente fortement la souplesse des UC câblées. De plus, les logiciels EDA facilitent la conception d'UC câblées de plus en plus complexes. L'utilisation des PLD permet l'intégration d'UC câblée fonc-

tionnant à fréquence élevée. Leur modification est relativement facile et automatisée par l'utilisation des logiciels EDA

Une UC est dite "microprogrammée" lorsque son comportement est essentiellement déterminé par un programme contenu dans une mémoire. Tant que l'on n'augmente pas le nombre d'entrées ou le nombre de sorties, et que le nombre d'instructions composant le programme ne dépasse pas la capacité de la mémoire et du générateur d'états prévus, le comportement peut être modifié par la simple reprogrammation de la mémoire (si elle est effaçable, sinon il faut programmer un autre IC) sans toucher au câblage.

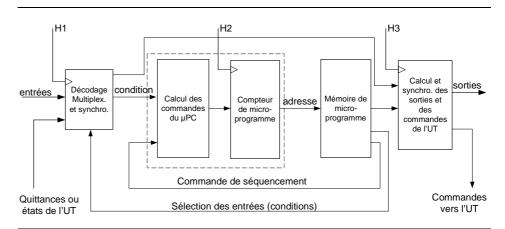

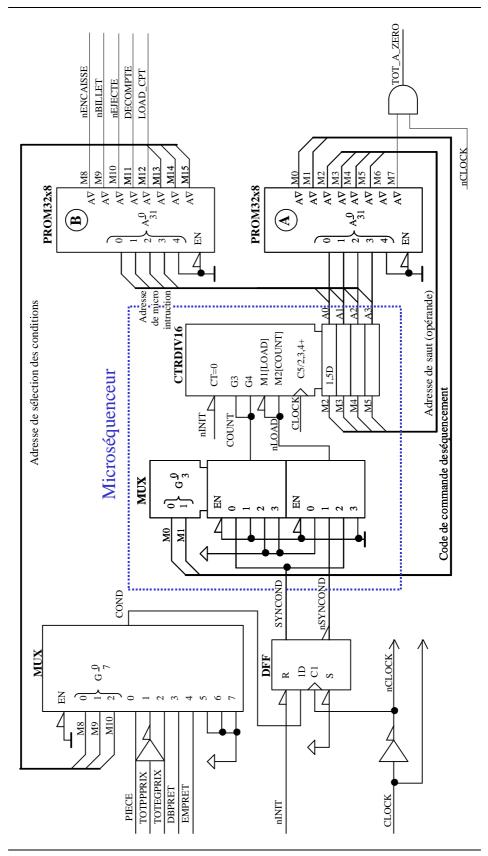

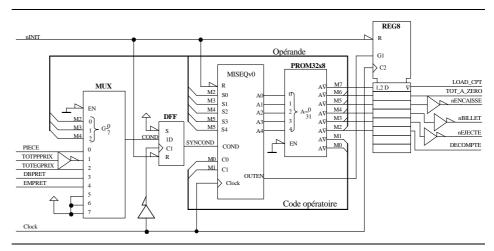

Le schéma-bloc d'une UC microprogrammée apparaît à la figure 1- 5. Ce schéma-bloc ne prétend pas couvrir toutes les structures possibles d'UC microprogrammées, mais il fait apparaître les caractéristiques distinctives d'une UC microprogrammée simple.

Le bloc de décodage-multiplexage-synchronisation des entrées et des quittances de l'UT est similaire à celui d'une UC câblée. Toutefois les commandes de sélection des conditions de séquencement ne proviennent généralement pas directement de l'état de la séquence, mais plutôt de la mémoire du microprogramme.

Figure 1-5: Schéma bloc d'une UC microprogrammée

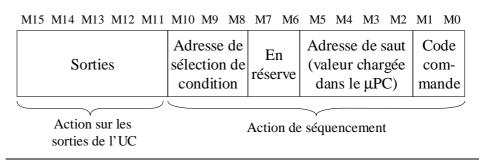

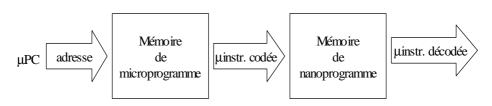

Les deux blocs regroupés dans un traitillé constituent ce que l'on appelle un micro-séquenceur. Son rôle est de générer l'adresse de la prochaine microinstruction, en fonction de la commande de séquencement et de l'entrée de condition (il n'y a normalement qu'une entrée de condition, connectée à la sortie du multiplexeur de conditions). Le bloc de calcul des commandes du uPC décode les commandes de séquencement provenant de la microinstruction en cours et en tire les signaux de commande du uPC, tenant comp-

te de l'entrée de condition. Le compteur de microprogramme est ainsi appelé parce que ce bloc, qui mémorise l'état de la séquence, a généralement un fonctionnement correspondant à celui d'un compteur.

Chaque état généré par le microséquenceur est utilisé comme une adresse pour aller chercher dans la mémoire de microprogramme la prochaine microinstruction à exécuter. Les microinstructions se décomposent en commandes de séquencement, généralement codées et comportant quelques bits utilisés pour sélectionner une condition (à travers le MUX des conditions), et en commandes destinées à gérer l'unité de traitement et à générer des sorties. Le bloc de calcul et sychronisation des sorties et des commandes de l'UT est similaire à celui d'une UC câblée.

#### Structure de l'unité de traitement

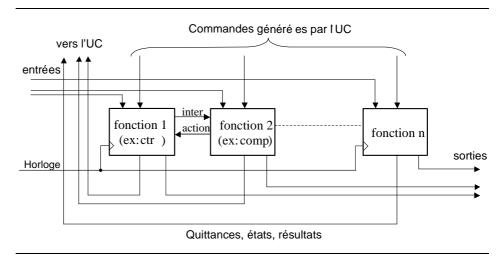

Dans une machine complexe décomposée en une unité de commande et une unité de traitement, l'uité de traitement effectue l'essentiel des opérations standard de traitement de l'information. Ces opérations ou fonctions standard peuvent être réalisées à l'aide de circuits spécialisés, que ce soit des circuits spécialisés standard (tels que des compteurs ou multiplexeurs) ou surtout des réseaux logique programmables (PLDs), ou à l'aide de circuits universels effectuant toutes les opérations élémentaires dans lesquelles nous pourrons décomposer n'importe quel traitement. Nous avons ainsi deux types de structures : les UT dites "spécialisées" ou "câblées" et les UT dites "universelles" ou "programmables".

Comme une UC câblée, une UT spécialisée est spécifiquement conçue pour une certaine machine complexe. Tout changement de fonctionnement demande une reconception du circuit et des modifications dans le câblage. Plus le traitement désiré est complexe, plus il comporte de fonctions, et plus volumineuse sera la circuiterie de l'UT.

Depuis l'apparition des PLDs et des outils de CAO associés, des UT performantes et complexes peuvent être réalisées dans une structure spécialisée, tout en conservant une grande souplesse d'adaptation et des dimensions très compactes. L'utilisation d'un langage de description de haut niveau tel le VHDL, permet une très forte réutilisation de fonction ou opérations. Le schéma-bloc de la figure 1- 6 illustre la structure d'une UT spécialisée. Les fonctions standard ou quasi-standard sont commandées individuellement par l'UC, mais peuvent également interagir entre elles. Certaines seront de nature purement combinatoire, d'autres de nature séquentielle.

Figure 1-6: Schéma bloc de la structure d'une UT spécialisée

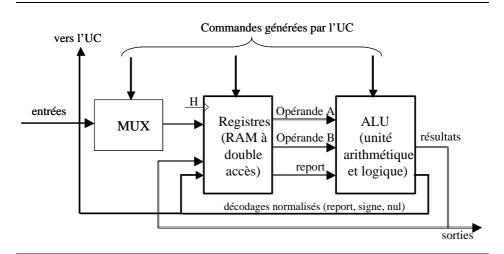

Une UT universelle repose sur le fait qu'une fonction combinatoire quelconque peut être décomposée en une suite de fonctions élémentaires (ET, OU et inversion logique, plus l'addition arithmétique), et qu'une fonction séquentielle quelconque peut être obtenue à l'aide d'un registre et d'une fonction combinatoire.

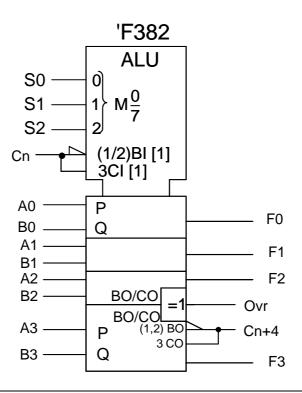

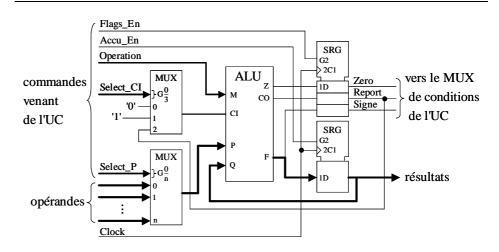

Les diverses fonctions élémentaires combinatoires, arithmétiques ou logiques, sont regroupées dans une unité appelée "unité arithmétique et logique" ou ALU (pour "Arithmetic Logic Unit", en anglais). Cette ALU comporte deux entrées d'opérandes (les informations d'entrée sur lesquelles elle doit effectuer une certaine opération, comme par exemple une addition), une entrée permettant de choisir l'opération à effectuer et une sortie pour le résultat. Chacune de ces entrées et sortie comporte normalement plusieurs bits.

La figure 1-7 nous montre un schéma-bloc très simplifié d'une UT universelle. Puisque tous les traitements de l'information se font à travers l'ALU, en séquence, c'est l'UC qui est chargé d'aiguiller les résultats de l'ALU vers les sorties concernées de la machine complexe.

Figure 1-7: Schéma bloc simplifié d'une UT universelle

Des informations d'entrée et des résultats intermédiaires sont mémorisés dans les registres. En plus du résultat d'une opération arithmétique ou logique, l'ALU fournit également des décodages normalisés qui sont : le report résultant d'une opération arithmétique, le signe du résultat, le fait que le résultat soit nul, et le fait que le résultat requière plus de bits que n'en comporte la sortie de l'ALU (dépassement de capacité). Ces décodages normalisés, appelés bits d'état de l'ALU, sont connectés au multiplexeur de conditions de l'UT.

Comme son nom l'indique, une même unité de traitement universelle peut être utilisée pour effectuer n'importe quel traitement de l'information aussi complexe soit-il. Toutefois, plus le traitement est complexe et plus il prendra de temps, du fait de sa décomposition en une séquence d'opérations élémentaires. Pour modifier le comportement d'une machine complexe utilisant une UT universelle, il suffit de modifier l'unité de commande. Si celle-ci est micropogrammable, une simple modification du microprogramme suffira s'il n'est pas nécessaire d'augmenter la taille de la mémoire de microprogramme, le nombre d'entrées ou le nombre de sorties.

#### Combinaison des structures d'UC et d'UT

Avec les deux structures de base définies pour les UC d'une part et les UT d'autre part, nous obtenons quatre combinaisons UC+UT possibles:

- 1)UC câblée et UT spécialisée

- -avec circuits discrets (exemple TTL): pratiquement plus utilisé.

- -avec PLD, très utilisé depuis l'arrivée de PLD "Low cost".

- 2)UC microprogrammable et UT spécialisées

#### 3)UC câblée et UT universelles

## 4)UC microprogrammable et UT universelles

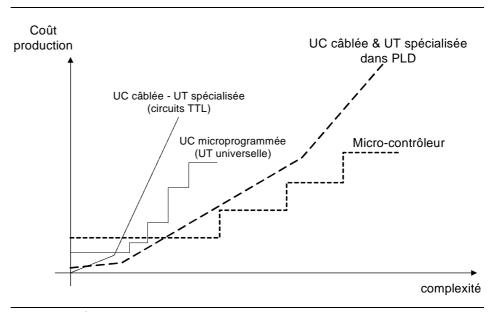

La combinaison UC câblée – UT spécialisée est celle qui permet d'atteindre les plus grandes performances. Son coût, que ce soit le coût de développement ou le coût de fabrication, est quasiment proportionnel à la complexité du traitement de l'information désiré. Cette combinaison sera donc utilisée pour des machines séquentielles de faible à moyenne complexité, ou pour des machines à hautes performances. L'apparition de PLD "Low cost" avec des performances très élevées rend cette combinaison très intéressante. Il est possible d'obtenir des fréquences de fonctionnement très élevées. Dans le cas de systèmes de faible complexité, les coûts peuvent être très compétitifs.

Le coût de développement d'une UC microprogrammée est inférieur à celui d'une UC câblée. Par contre, son coût de production augmente de façon incrémentale avec la complexité. La figure 1- 8 compare les courbes de coût d'une UC câblée et d'une UC microprogrammée.

Figure 1-8: Évolution du coût de production en fonction de la complexité

Une UC microprogrammée est un système modulaire, ce qui explique la courbe de coût en escalier. La courbe de coût d'une UC câblée comporte aussi des escaliers, mais de plus faible amplitude (non représenté). Dans le début de la courbe, l'augmentation de complexité résulte dans l'utilisation d'un circuit programmable plus complexe. La pente augmente dès qu'il est

nécessaire d'intégrer l'UC câblée dans un PLD de plus grande capacité ou dans plusieurs PLD.

Le point de croisement des deux courbes évolue avec l'apparition de nouveaux circuits et l'évolution du marché. Le point est aussi différent selon la fréquence de fonctionnement.

Le fonctionnement d'une UC microprogrammable sera plus lent que celui d'une UC câblée. La combinaison UC microprogrammable – UT spécialisée convient donc pour les machines d'un niveau de performance et de complexité moyen.

Le coût de développement d'une UT universelle est inférieur à celui d'une UT spécialisée. Par contre, les coûts de production ont des courbes comparables à celles de la figure 1-8: celle d'une UT spécialisée est similaire à celle d'une UC microprogrammée.

Les performances atteintes à l'aide d'une UT universelle sont faibles, du fait de la décomposition de tout travail en une séquence d'opérations élémentaires. Ainsi, la combinaison d'une UC câblée et d'une UT universelle n'a guère d'intérêt.

En combinant une UC microprogrammée et une UT universelle, nous obtenons un maximum de souplesse et un coût favorable pour les hautes complexités. Les performances seront par contre les plus faibles des quatre combinaisons. C'est pourtant la structure utilisée dans la plupart des microprocesseurs. La combinaison UC microprogrammée avec une UT universelle correspond à la structure d'un processeur. Celui-ci comprend une unité de séquencement qui traite les instructions du programme. Le processeur est capable de faire des opérations qui sont réalisées dans l'ALU(Arithmetic Logic Unit) interne à celuil-ci. Il s'agit d'une UT universelle.

La disponibilité de PLDs de grande capacité permet l'intégration d'un processeur complet. Il existe actuellement des descriptions, en langage HDL (tel le VHDL), fournie par les vendeurs de PLD. L'UC pourra donc être remplacée par un processeur avec un programme écrit en langage assembleur, voir même de haut niveau (exemple "C"). Il s'agit d'une nouvelle possibilité de réaliser des MSS complexes.

## Chapitre 2

## Méthode de conception

Le fonctionnement d'une machine séquentielle conçue en séparant UC et UT résulte d'un algorithme implémenté par l'UC. De telles machines sont donc appelées "machines algorithmiques" (ou ASM, pour "Algorithmic State Machine" en anglais). L'établissement d'un algorithme de fonctionnement va être l'étape la plus importante dans la conception d'une machine algorithmique.

La méthode de conception est de type descendant ("top-down"): on commence par une approche globale, pour aborder progressivement des détails de plus en plus fins. Les étapes principales de la méthode sont listés ci-dessous, par ordre chronologique.

1) Établir les spécifications ou, si elles sont déjà données, les étudier d'un oeil critique pour s'assurer qu'elles sont complètes, qu'elles correspondent bien aux besoins à couvrir, et qu'elles n'introduisent pas des contraintes superflues.

- 2) Définir les relations temporelles désirées liant les entrées et les sorties de notre machine, ceci à l'aide de chronogrammes. Prendre aussi note de toute les contraintes spéciales de fréquence, débit d'information ou temps de réponse.

- 3) Décrire le système dans lequel s'insère notre machine sous la forme d'un schéma-bloc grossier faisant apparaître les échanges d'information, et le comportement de notre machine sous la forme d'une algorithme général. Celui-ci décrira le comportement à l'aide de phrase, texte...

- 4) Détailler progressivement l'algorithme de fonctionnement, de façon à faire apparaître des fonctions standard ou d'autres sous-machines. Durant cette phase, l'organigramme sera affiné, évolué.

- 5) Choisir la structure de l'unité de traitement la mieux appropriée, étant donnée les fonctions standard apparaissant dans l'algorithme, le niveau global de complexité, les performances à atteindre (définies en particulier au point 4), le temps de développement et le coût visé. Établir un schémabloc donnant les fonctions principales de cette unité de traitement.

- 6) Choisir la structure la mieux appropriée pour l'unité de commande, en tenant compte de la taille et de la complexité de l'algorithme à implémenter, de la vitesse de fonctionnement, du temps de développement et des impératifs économiques. Établir un schéma-bloc de cette unité de commande, faisant clairement apparaître toutes ses entrées et toutes ses sorties.

- 7) Choisir les principaux composants (circuits intégrés) à utiliser, aussi bien pour l'UC que pour l'UT, et vérifier que les objectifs visés sont atteignables.

- 8) Finir la conception de l'UT aboutissant à des schémas et des fichiers de description VHDL pour les PLDs. Tester l'UT.

- 9) Finir la conception de l'UC, aboutissant à des schémas, des fichiers de description VHDL pour les PLDs et des fichiers de programmation pour les mémoires. Tester l'UC, puis la machine complète.

L'étape 1 relève d'avantage de la conduite de projets que de l'électronique numérique et ne sera donc pas étudiée dans le cadre de ce cours. Les autres étapes seront traitées à l'aide d'exemples dans ce qui suit. Les choix

de structure dans les étapes 5 et 6 demandent de bonnes connaissances des circuits disponibles et seront donc laissés à l'ingénieur expérimenté.

Le test, en particulier le test de fabrication, est un gros problème en soi. Bien qu'il ait une influence importante sur la conception d'une machine, nous le traiterons séparément au chapitre IX.

Jusqu'au point 7 y-compris, la méthode ci-dessus est aussi valable pour le développement de machines basées sur un microprocesseur. En fait, si nous avons choisi une UT universelle et une UC microprogrammée, nous utiliserons plutôt un système à microprocesseur. Dans ce cas, les dernières étapes sont l'établissement du schéma puis l'écriture d'un programme.

## **Chapitre 3**

# Application de la méthodologie de conception à la multiplication

Pour présenter la démarche de conception d'une machine séquentielle complexe, nous allons utiliser la multiplication binaire. Pour cet exemple, nous allons utiliser 2 nombres entiers non-signés de 4 bits. Le résultat sera donné sur 8 bits. Nous allons nous appuyer sur l'étude faite, dans le chapitre précédent, de la multiplication non-signée.

## 3-1 Spécification de la multiplication séquentielle

Nous allons utiliser une multiplication avec une décomposition séquentielle. Cette exemple permettra de mettre en évidence les tâches gérées par l'UC et les opérations réalisées par l'UT.

Voici la spécification du fonctionnement de la multiplication séquentielle, soit:

-Lors d'une transition de '0' à '1' du signal START, le calcul de la multiplication est démarré. À cet instant, les valeurs du Multiplicateur et du

Multiplicande sont disponibles en entrée. Le calcul utilisera le principe de la décomposition temporelle.

-Lorsque la multiplication est terminée, le signal Done est activé. Le résultat est disponible tant que Done reste actif.

## Schéma-bloc général

Les étapes 1 et 2 de la méthode de conception ont été traité dans le chapitre qui précède.

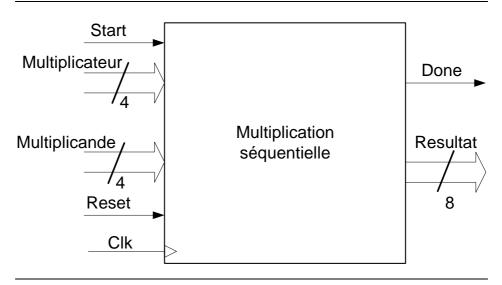

Pour notre exemple, nous pouvons donc passer à l'étape 3 et établir un schéma-bloc général. Celui-ci est représenté à la figure 3-1. Le système de commande que nous devons développer apparaît comme un seul bloc, le but étant de montrer comment il est relié aux autres parties de l'appareil. Tout découpage plus détaillé serait prématuré, et ne pourrait résulter que d'à-prioris qu'il faut absolument éviter pour être en mesure par la suite de faire librement les meilleurs choix.

Figure 3-1: Schéma-bloc général de la multiplication séquentielle

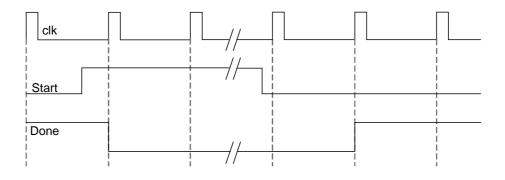

Le chronogramme de la figure 3- 2 nous donne le comportement des signaux Start et Done du système.

Figure 3-2: Chronogramme du fonctionnement

## Algorithme

La première phase de la conception consiste à établir un algorithme répondant au cahier des charges. Cet algorithme a été étudié lors du chapitre sur la numération et l'arithmétique. Voici celui-ci:

```

Resultat_Haut := 0;

for I=1 to Nombre_Bits

if LSB(Multiplicateur) = 1 then

Resultat_Haut := Resultat_Haut + Multiplicande;

(mémorisation du report dans un flip-flop)

else

Resultat_Haut := Resultat_Haut+0;

end if

Décalage à droite(Report, Resultat_Haut, Multiplicateur);

end for;

Resultat_Bas := Multiplicateur;

Resultat := Resultat_Haut & Resultat_Bas;

```

## 3-2 Algorithme : organigramme ou graphe

Lors de la conception des MSS simples, nous avons utilisé un graphe d'états pour décrire le comportement d'une machine séquentielle. En l'adaptant aux exigences liées au grand nombre d'entrées, de sorties et d'états, nous pouvons également l'utiliser pour décrire le comportement d'unités de commande câblées, dans les machines séquentielles complexes. Toutefois, un graphe d'états n'est guère pratique pour décrire un algorithme de fonctionnement général.

Dans ce qui suit, nous allons utiliser une autre forme de représentation graphique, appelée "organigramme" ("flow-chart" ou "flow diagram", en anglais), qui offre l'avantage d'être utilisable, non seulement pour décrire l'algorithme de fonctionnement général, mais aussi pour décrire une réalisation à l'aide d'un microprocesseur ou d'une unité de commande microprogrammée. Contrairement à un graphe d'états, un organigramme met l'accent sur la séquence des actions qu'il faut commander, plutôt que sur une séquence d'états. Une action pourra par la suite être une suite d'états ou nécessiter du matériel dans l'UT.

Un organigramme utilise les symboles graphiques suivants:

Une flèche, généralement pointant de haut en bas, illustre le passage d'une action à la suivante.

Déterminer la valeur de la pièce reçue

Une boîte rectangulaire désigne un ensemble d'actions ou opérations s'effectuant simultanément; par exemple : Initialisation de la variable I à zéro et activation du signal Done.

Une boîte en forme de losange ou d'hexagone désigne une condition binaire qui modifie le déroulement des opérations, selon que cette condition est remplie ou non

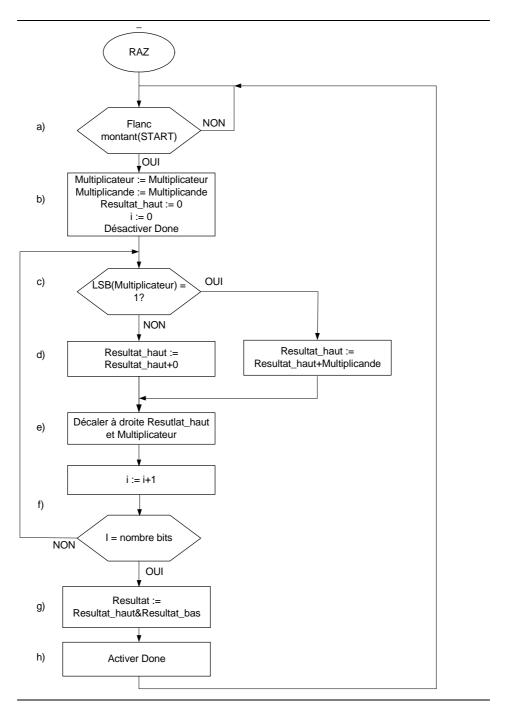

Nous allons débuter par représenter l'algorithme sous forme d'un organigramme. À partir de celui-ci, il est possible de réaliser la partition des tâches entre l'unité de traitement et l'unité de commande. Le premier organigramme sera nommé organigramme grossier de la multiplication séquentielle. Il ne comprend, dans les boîtes, que des **textes/actions ou fonctions générales**.

Nous allons maintenant présenter la construction de l'organigramme pour notre exemple.

Lors du démarrage de tout système séquentiel, une remise à zéro est indispensable. Dans l'organigramme grossier, l'action d'un Reset sera visualisée par une bulle arrondie avec RAZ. Le premier élément de l'organigramme est le test du flanc montant du signal start. Dès que le flanc a été détecté il faut initialiser les différentes valeurs. Il faut affecter aux variables Multiplicateur et Multiplicande les valeurs fournies en entrée. Resultat\_haut est initialisé à "0000". La variable de boucle i est initialisée à 1 et le signal de sortie Done devient inactif.

Ensuite, le teste de l'état du bit LSB de Multiplicateur détermine s'il faut effectuer l'addition de Resultat\_haut avec le Multiplicande ou maintenir la valeur de Resultat\_haut. Cette dernière opération est équivalente à additionner 0. L'opération suivante décale Resultat\_haut et Multiplicateur sur la droite.

Il faut incrémenter le compteur de boucle afin de comptabiliser le traitement d'un bit du multiplicateur. Il faut ensuite tester si la variable de boucle i a atteint la valeur nombre\_bits (dans notre cas 4). Si cette valeur est atteinte il faut concaténer Resultat\_haut avec Resultat\_bas. Resultat\_bas et Multiplicateur sont contenu par la même variable. Dans le cas où la variable i n'a pas atteint 4, retourner au test du LSB de Multiplicateur.

On termine le cycle en activant le signal Done qui indique que la multiplication est terminée. Pour recommencer l'opération il faut attendre un nouveau flanc montant sur le signal Start.

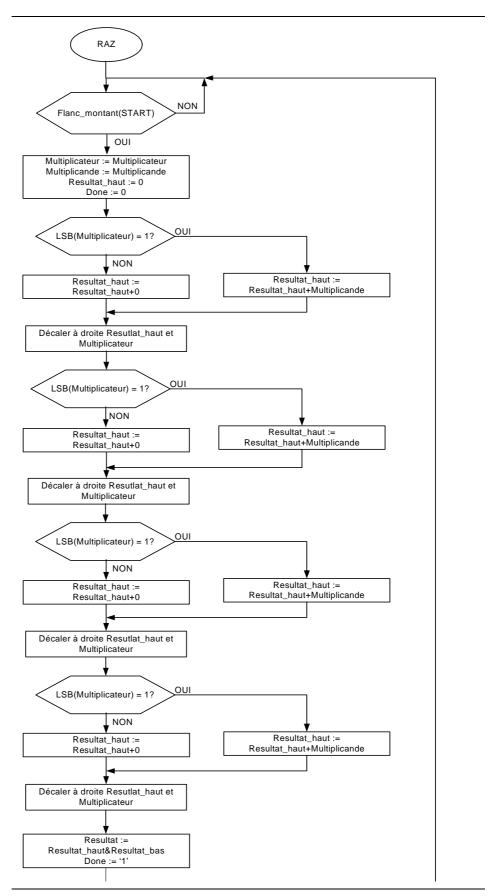

Figure 3-3: Organigramme grossier de la multiplication séquentielle

## 3-3 Partition unité de commande / unité de traitement

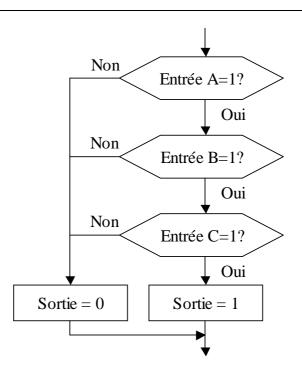

La décomposition d'une machine complexe en une unité de commande et une unité de traitement est l'élément clé de notre méthode de conception. Cette décomposition laisse une grande place à l'imagination, à l'expérience et au savoir faire du concepteur, relevant donc plus de l'art que de la science. Lors de chaque choix que nous aurons à faire, il ne faut jamais perdre de vue que toute fonction combinatoire, de la plus simple à la plus complexe, peut être décomposée en une séquence. Par exemple, le bout d'organigramme de la figure 3- 4 réalise une fonction ET à 3 entrées.

Figure 3-4: Organigramme de la fonction logique ET à 3 entrées

En utilisant les annotations visibles sur l'organigramme grossier de notre exemple (figure 3- 3), nous allons identifier les fonctions à effectuer dans l'unité de traitement ou dans l'unité de commande. Nous allons traiter les boîtes les unes après les autres.

- a) La détection d'un flanc sera réalisée en testant l'état de l'entrée Start dans l'UC. Il n'y a pas besoin de matériel dans L'UT.

- b) Ce bloc comporte l'initialisation des différentes valeurs utilisées dans la multiplication. L'équivalent d'une variable dans l'UT est un registre. Multiplicateur (Resultat\_bas), Multiplicande et Resultat\_haut seront donc contenus dans des registres. Ceux-ci seront placés dans l'UT. Ils n'interviennent pas dans le séquencement. Nous choisissons d'intégrer la variable de boucle dans l'UC. Il s'agit de répéter 4 fois l'opération de traitement d'un bit du Multiplicateur.

- c) La valeur de Multiplicateur (Resultat\_bas) se trouve dans l'UT. Pour tester le bit LSB, il faut relier celui-ci à l'UC, nous appellerons ce signal LSB\_Mteur.

- d) La réalisation de l'addition sera commandée par l'activation d'un chargement du résultat de l'addition. Selon le résultat du test de LSB (voir point b), on additionne Resultat\_haut avec Multiplicande ou avec zero, correspondant aux deux chemins définis dans l'organigramme.

Remarque: Il est à noter que le signal du chargement du registre contenant Resultat\_haut devra être distingué des autres registres (Load). Ces signaux proviennent de l'UC.

- e) Pour décaler ces deux valeurs, nous allons utiliser des registres à décalage. Ces registres se trouvent dans l'UT et sont commandés par un signal provenant de l'UC (Decale).

- f) Afin d'éliminer un compteur de boucle, nous avons choisi de dérouler la boucle de l'organigramme. Ceci implique de répéter 4 fois la séquence des opérations pour chaque bit du Multiplicateur dans l'organigramme.

- g) L'UT doit fournir le résultat final de la mltiplication. Il faut simplement concaténer les deux registres Resultat\_haut et Resultat\_bas. Il s'agit de simple fils!.

- h) Cette sortie sera activée directement par l'UC. L'activation de ce signal indique que le résultat final est valide. Nous regroupons ces deux dernières boites qui sont liées.

Suite à la partition, nous obtenons l'organigramme évolué (figure 3-5) représentant la suite d'opérations gérées par l'UC.

Figure 3-5 : Organigramme évolué

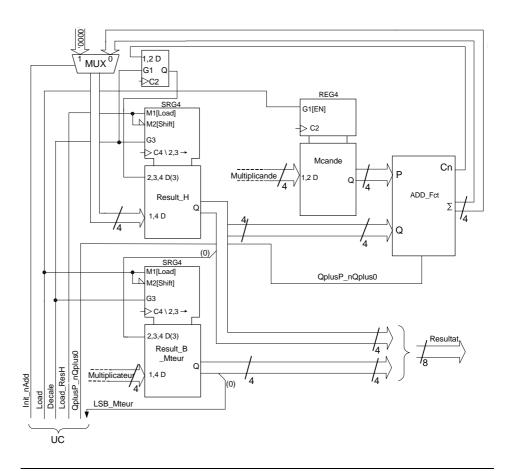

## Identification des fonctionnalités de l'UT

Le partitionnement UC/UT détermine les fonctions qui se trouveront dans l'UT. Il faut maintenant identifier l'ensemble des fonctions à implémenter dans l'UT.

L'UT comportera un additionneur commandé par le signal QplusP\_nQplus0 afin d'additionner Resultat\_haut avec Multiplicande ou avec zero. Les deux entrées P et Q comportent chacune 4 bits. Il les additionne de manière asynchrone, le résultat comporte 4 bits ainsi qu'un bit de report pour le dépassement.

Le décalage étant effectué après le chargement du résultat dans le registre contenant Resultat\_haut, il faut s'assurer que le bit de report soit encore disponible au moment du décalage. Mais, dès que le registre contenant Resultat\_haut a enregistré le résultat de l'addition, sa sortie change. Donc les valeurs de sorties de l'additionneur changent. La valeur du report n'est plus la même. Il faut donc mémoriser celui-ci dans une bascule (DFF) pour l'opération de décalage exécutée lors du cycle suivant.

Les 4 bits du Resultat\_haut sont stockés dans un registre à décalage de 4 bits. Ce registre s'appelle Result\_H. Le bit entrant provient de la bascule contenant le report de l'additionneur. Et le bit sortant est repris par Result\_B\_Mteur. Sa sortie de 4 bits est reliée à une des entrées de l'additionneur. Le registre charge le résultat de l'addition lorsque le signal Load\_ResH est active. Le décalage de la valeur est activé par le signal Decale.

Lors de l'initialisation, il faut charger Result\_H avec la valeur "0000". Mais son entrée doit aussi charger le résultat de l'addition. C'est pour cette raison qu'il faut utiliser un multiplexeur,il sélectionne la valeur "0000" uniquement à l'initialisation. Le multiplexeur est commandé par le signal Init\_nAdd.

Les 4 bits de Resultat\_bas (Multiplicateur) sont stockés dans un registre à décalage de 4 bits. Ce registre s'appel Result\_B\_Mteur. Il est identique au registre Result\_H. Le bit entrant provient du registre à décalage de Result\_H. Le bit sortant est perdu. Le contenu de ce registre est chargé à l'initialisation avec la valeur de Multiplicateur fournie au système. Le décalage de la valeur est activé par le signal Decale et le chargement de la valeur par le signal Load (actif lors de la remise à zéro du système). Le contenu du registre représente les 4 bits de poids faible du résultat final.

Les 4 bits de Multiplicande sont contenu dans un registre qui se nomme Mcande. Ce registre est chargé une fois à l'initialisation avec la valeur Multiplicande fournie au système. La sortie du registre est reliée à une des entrée de l'additionneur.

Pour concaténer les 4 bits de Result\_H avec les 4 bits de Result\_B\_Mteur, il suffit de les regrouper afin de former les 8 bits de Resultat.

## Unité de traitment

En résumé l'unité de traitement comporte les composants suivants:

- 2 registres, Result\_H et Result\_B\_Mteur, avec chargement parallèle et décalage à droite

- 1 registre, Mcande, avec chargement parallèle

- 1 additionneur de 4 bits avec report

- 1 multiplexeur 2 à 1 sur 4 bits pour sélectionner la valeur de chargement pour le registre Result\_H

- 1 bascule DFF pour mémoriser le report

Figure 3-6: Unité de traitement

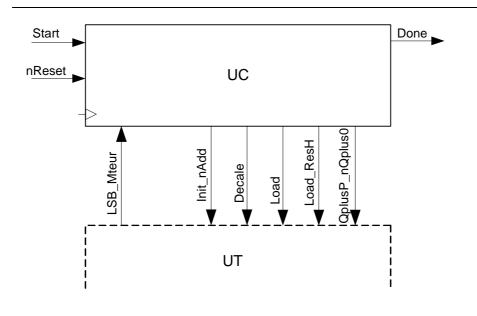

#### Unité de commande

L'unité de commande gère les signaux de contrôle de l'UT. Il s'agit des signaux Load, Load\_ResH, Decale et LSB\_Mteur. Elle gère aussi les signaux de sortie du système soit Done. Les signaux d'entrée Start et nReset aggissent aussi sur l'UC. La figure 3-7 nous montre l'ensemble des signux connectés sur l'UC.

Figure 3-7: Unité de commande

## 3-4 Passage d'un organigramme à un graphe

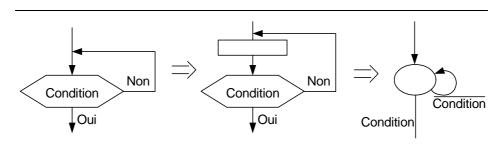

Si nous détaillons suffisamment un organigramme décrivant le comportement d'une machine séquentielle, nous arriverons à ce que chaque boîte d'action ne contienne que des actions pouvant être effectuées dans une seule et même période d'horloge. Dans ce cas, chaque boîte d'actions correspond à un état interne de la machine séquentielle, soit une bulle dans le graphe d'états.

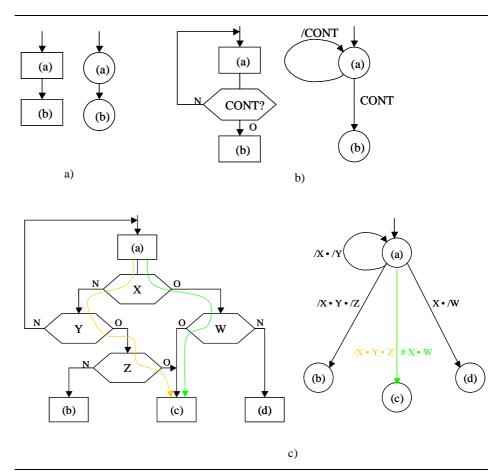

Intuitivement, on comprend aisément qu'il y a une parfaite correspondance entre un organigramme et un graphe d'états. Sans nous attarder à des démonstrations oiseuses, nous utiliserons les règles suivantes:

règle n°1: Une boîte d'actions dans un organigramme détaillé définit un état dans le graphe. Une état commence au début d'une boîte d'actions et se termine à l'entrée de la boîte d'actions suivante, quel que soit le chemin parcouru à travers des boîtes de condition. La figure 3- 8 donne des exemples de passage d'un organigramme à un graphe. Ll'extrait d'organigramme de la figure 3- 8(c) contient quatre états: (a), (b), (c) et (d), l'état (a) englobant toutes les boîtes de condition.

Figure 3-8: Passage d'un organigramme à un graphe

règle n°2: Les conditions d'entrée qui font passer d'un état à un autre dans un graphe peuvent être retrouvées dans un organigramme en suivant les chemins possibles à travers les boîtes de condition entre deux boîtes d'actions.

La figure 3-8(c) met en évidence les différents chemins qui mènent de l'état (a) aux états (b), (c) ou (d), ainsi que les différentes conditions dont dépendent ces transitions.

Dans une MSS ayant beaucoup de variables d'entrée (c'est le cas si cette MSS est une unité de commande d'une machine complexe), il est évident qu'il ne faut pas mettre une flèche dans le graphe pour chaque combinaison des variables d'entrée, à partir de chaque état. Désormais, nous reporterons sur une flèche non pas une combinaison des variables d'entrée, mais l'ex-

pression logique représentant la condition (complexe) qui entraîne cette transition. Cela nous permettra de ne représenter qu'une seule flèche pour toutes les possibilités de passer d'un état (a) à un état (b), où (b) est l'état futur de (a).

Ainsi que nous l'avons vu lors du chapitre sur les MSS simples, les entrées asynchrones (qui ne changent pas en synchronisme avec l'horloge) peuvent nous poser des problèmes. Il est dès lors judicieux de les mettre en évidence, en les signalant par un astérisque ('\*'), par exemple.

règle n°3: Les tests portant sur une entrée asynchrone seront signalés dans un organigramme à l'aide d'un astérisque placé dans la boîte de condition correspondante. De même, dans un graphe un état dont l'évolution dépend d'entrées asynchrones sera signalé par un astérisque.

règle n°4: Les changements d'état des sorties, ou l'activation des sorties doivent être indiqués par des actions dans l'organigramme. Nous distinguerons les sorties ou actions inconditionnelles, c'est-à-dire ne dépendant que de l'état interne du séquenceur (rappel : séquenceur = UC), des sorties conditionnelles, c'est-à-dire dépendant également d'une ou plusieurs entrées.

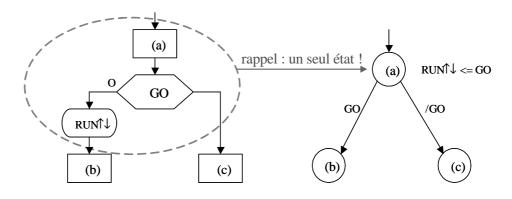

Dans un organigramme, les sorties conditionnelles apparaissent dans des boîtes d'action de forme oblongue, alors que les sorties inconditionnelles se trouvent dans des boîtes rectangulaires, comme nous le montre la figure 3- 9 où la sortie RUN dépend de l'entrée GO.

Figure 3-9: Mise en évidence des sorties conditionnelles et inconditionnelles

Une sortie conditionnelle ne définit pas un nouvel état. Dans l'exemple de la figure précédente, la sortie RUN est activée pendant l'état (a) lorsque l'entrée GO est active, d'où la notation utilisée dans le graphe: la sortie est indiquée à côté de l'état dans lequel elle sera active, à l'aide d'une expression partielle, soit RUN ??= (a) & GO dans cet exemple.

Il arrive fréquemment qu'une sortie doive être mise à l'état actif lorsque l'UC est dans un certain état de la séquence, puis soit maintenue à l'état actif jusqu'à ce que l'UC atteigne un certain autre état. C'est la raison pour la-

quelle une action a lieu: 99?? pour une impulsion à l'état actif, ??pour une impulsion à l'état inactif, ?pour l'activation, ?pour la désactivation. Lorsque l'activation et la désactivation d'une sortie ne se font pas dans le même état de l'UC, il faut soit maintenir celle-ci dans tous les états intermédiaires soit conserver la valeur de la sortie, entre deux changements, à l'aide d'une bascule (UT).

## Remarque importante

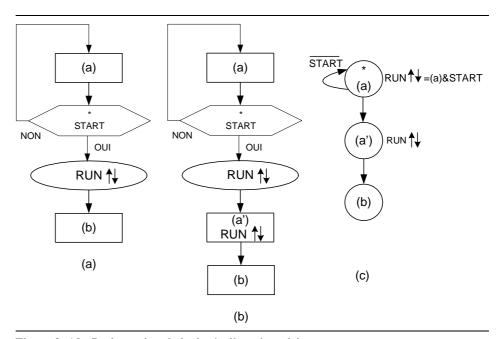

Il faut éviter de créer des sorties conditionnelles dépendant d'une entrée asynchrone, à cause de la possibilité d'avoir une impulsion de sortie de durée infinitésimale. Si cela ne peut pas être évité, il faut s'assurer que l'état actif ou inactif de l'entrée dure plus d'une période d'horloge (afin qu'elle soit vue dans cet état lors du flanc actif de l'horloge) et introduire un état supplémentaire pendant lequel cette impulsion sera prolongé. Ainsi, l'organigramme de la figure 3- 10 (a) doit être adapté comme l'indique la figure 3- 10 (b), d'où le graphe de la figure 3- 10 (c). Les codes des états (a) et (a') doivent bien sur être adjacents.

Figure 3-10 : Prolongation de la durée d'une impulsion

Le problème est le même lorsque ce n'est pas le début mais la fin d'une impulsion de sortie qui dépend d'une entrée asynchrone. Dans ce cas, on ajoutera l'état supplémentaire avant l'état dans lequel l'impulsion se termine. Cette situation est illustrée par la figure 3-11.

Figure 3-11 : Ajout d'un état supplémentaire

Lorsqu'une boîte de test est rebouclée sur elle-même, il est nécessaire de rajouter un état dans la boucle.

Figure 3-12 : Adaptation d'une boîte de test rebouclée

## 3-5 Organigramme détaillé

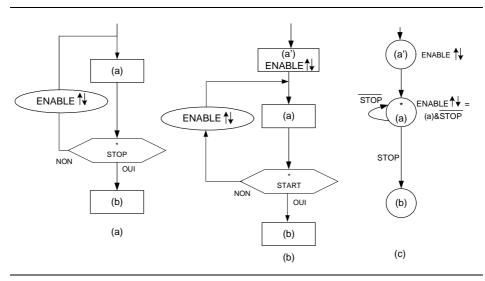

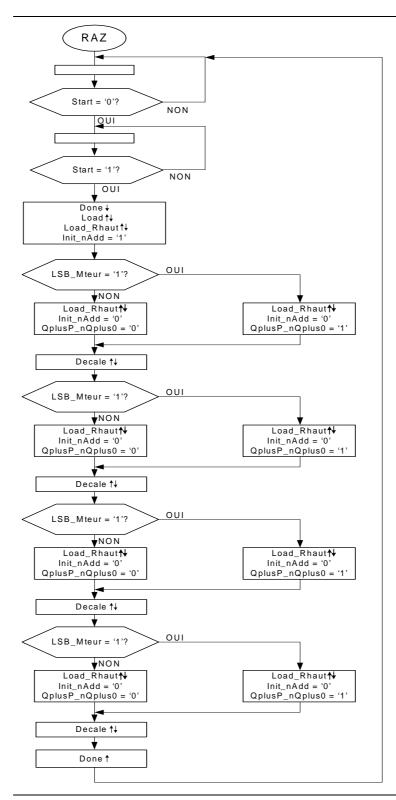

En tenant compte de l'unité de traitement et de l'organigramme de l'UC de la figure 3-11, il est maintenant possible d'établir un organigramme détaillé. L'organigramme détaillé représente l'organigramme grossier en intégrant la partition choisie pour l'UT et l'UC. Cet organigramme contient uniquement les signaux connectés sur l'UC. Nous allons présenter l'évolution de l'organigramme de la figure 3-5 vers l'organigramme détaillé pour notre exemple de multiplication séquentielle.

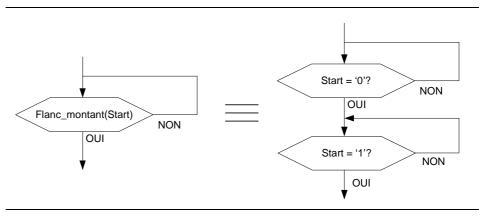

Le système est activé lorsqu'il y a un flanc montant sur le signal Start. La détection d'un flanc montant est réalisée en testant le signal Start à l'état bas puis à l'état haut. Le système peut-être démarré à la suite de ces deux tests.

Il est nécessaire de décomposer cette opération pour l'organigramme détaillé (figure 3- 13).

Figure 3-13 : détection du flanc montant. Organigramme grossier et détaillé

Le chargement du Multiplicateur et du Multiplicande s'effectuent en activant le signal Load. Le résultat est initialisé à zéro en mettant le registre Result\_H à zéro. Cette initialisation est réalisée en activant le signal Load\_ResH tout en ayant le signal Init\_nAdd actif ('1'). Le résultat de l'addition est chargé dans le Result\_H en activant le signal Load\_ResH. Le signal Init\_nAdd doit être inactif ('0').

Le décalage à droite de Result\_H et de Result\_B\_Mteur est effectué en activant le signal Decale.

Dans l'organigramme général, l'avant dernière opération consiste à concaténer Result\_H avec Result\_B. Dans l'organigramme détaillé, cette opération disparaît car cela est fait par l'UT (câblage).

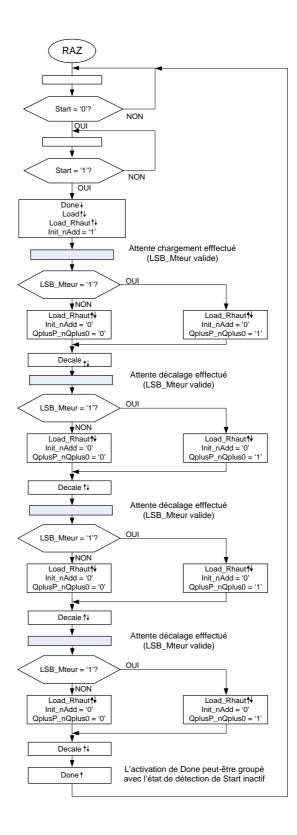

La figure 3- 14 présente l'organigramme détaillé pour notre exemple.

Figure 3- 14 : Organigramme détaillé de la multiplication séquentielle

Remarque: Le signal Init\_nAdd est utilisé seulement lorsque Load\_Rhaut est activé. Nous avons seulement indiqué le niveau requis pour les états concernés. Pour tous les autres états de l'organigramme le signal Init\_nAdd n'est pas spécifié (cas '-').

## 3-6 UC câblée

Une UC câblée peut être développée avec les méthodes étudiées précédemment pour autant qu'elle soit d'un niveau de complexité compatible avec les PLDs et les outils de CAO dont nous disposons. Avec les FPGA (réseaux matriciels), le niveau de complexité maximal est très élevé actuellement, et il augmente chaque année.

Dans un organigramme détaillé, chaque boîte d'action ne contienne que des actions pouvant-être effectuées dans une seule et même période d'horloge. Dans ce cas, chaque boîte d'action correspond à un état interne de la machine séquentielle, donc à une bulle dans le graphe d'états.

Il faut être attentif au fait qu'il n'est pas possible de tester un signal durant le même cycle d'horloge nécessaire à son établissement. Car durant ce cycle, l'état est en train de se modifier. Si on test cette valeur, on obtiendra une valeur erroné. Il faut donc attendre un cycle pour tester un signal.

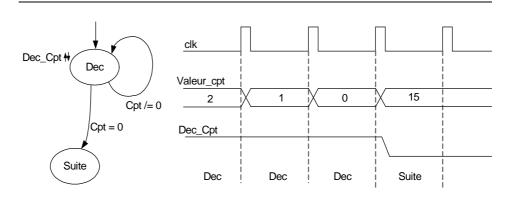

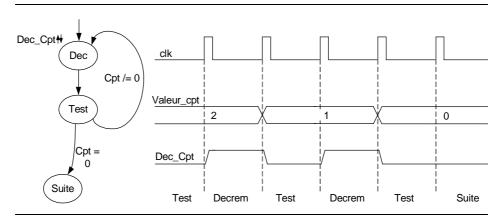

Prenons l'exemple d'un décompteur 4 bits. Nous souhaitons décompter celui-ci tant qu'il n'a pas atteint la valeur zéro. Sur le chronogramme de la figure 3-15, nous observons un fonctionnement incorrecte du décomptage. Lorsque nous sommes dans l'état suite, le compteur est finalement à l'état 15 et non 0 comme souhaité.

Sur la figure 3- 15, la condition de sortie de l'état Dec est pourtant bien Cpt=0. Lorsque cette condition devient active, nous passons, au prochain flan montant de l'horloge, dans l'état suite. Mais simultanément, le signal Dec\_Cpt est encore actif et le compteur est décrémenté encore une fois.

Figure 3-15: Fonctionnement incorrecte

Une solution à ce problème (figure 3-16) consiste à ajouter un état supplémentaire appelé "Test" durant lequel le signal activant la décémentation est inactif. Si le décompteur n'a pas atteint zéro, il faut retourner à l'état de décrémentation. Si la valeur du décompteur est égale à zéro, il faut passer à l'état suivant et la valeur du décompteur restera égale à zéro. Dans ce cas l'état final du compteur est correct.

Figure 3-16: Fonctionnement correcte

Suite à l'ensemble de ces considération, nous pouvons établir l'organifgramme final de notre UC. Celuic-i est donnée dans la figure 3-17.

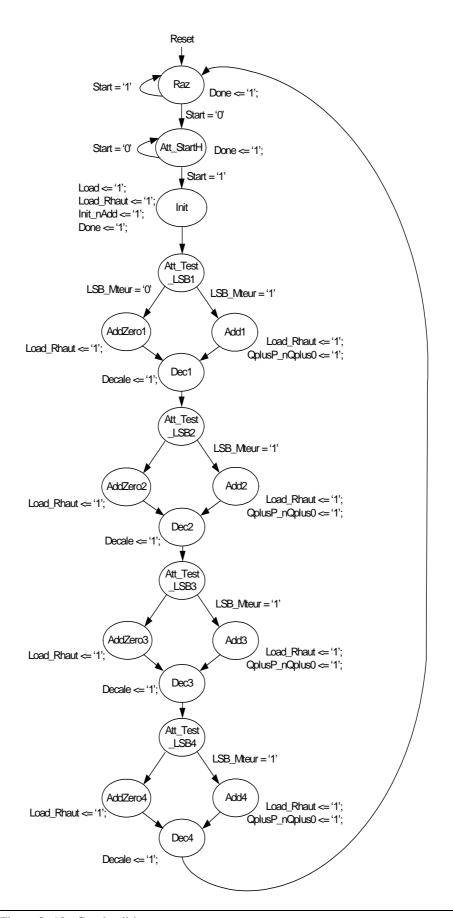

Nous allons établir un graphe (figure 3- 18) à partir de l'organigramme détaillé de la figure 3- 14, ce qui nous permettra de vérifier le découpage en états. Nous avons ajouté les Att\_Tst\_LSB afin de palier au problème décrit précédemment.

Dans la figure 3- 18, seul l'activation des sorties est indiquée. Par défaut, les signaux de sorties sont à l'état inactif. Pour le signal Init\_nAdd il y a des états où l'état de celui-ci est indifférent ('-'). Cela n'est pas indiqué dans le graphe de la figure 3- 18. Il y a une possibilité d'optimisation non exploitée dans cette version de graphe des états.

Figure 3-17: Organigramme détaillé final de la multiplication séquentielle

Figure 3-18: Graphe d'états

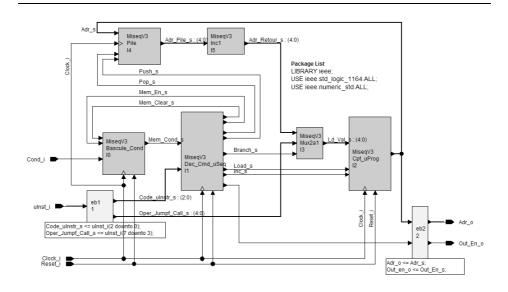

### Decription VHDL de l'UC câblée

## 3-7 Exercices

- 1) Réaliser une version permettant la multiplication de deux nombres de n bits. Proposer une modification de l'organigramme et les évolutions de l'UT.

- 2) Etablir le graphe des états correspondant à l'exercice précédent (1.) Puis proposer une optimisation du décodeur de sorties sachant que les signaux Init\_nAdd et QplusP\_nQplus0 ne sont pas toujours utilisés.

- 3)Trouver un moyen de supprimer le coup d'horloge nécessaire au décalage. Dans la version proposée, il faut 2 coups d'horloge. Le premier mémorise le résultat du calcul, le second réalise le décalage. Proposer une modification permettant de faire ces deux opérations en un coup d'horloge.

- 4) Etablir le graphe des états correspondant à l'exercice 3.

# **Chapitre 4**

# Exemple :Distributeur automatique de billets

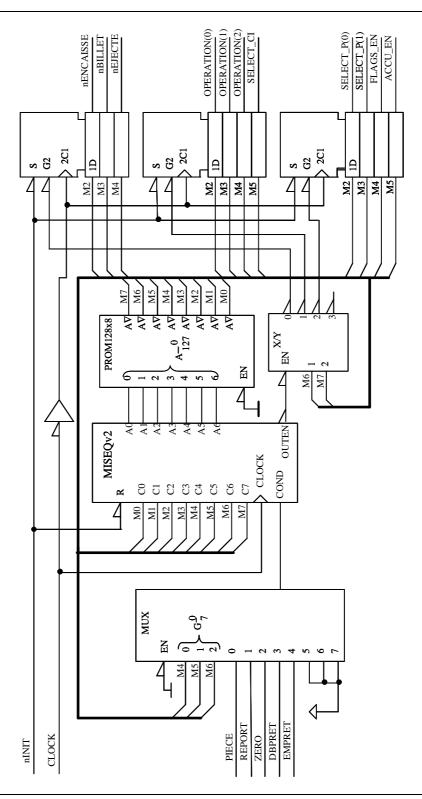

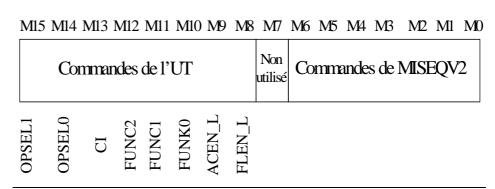

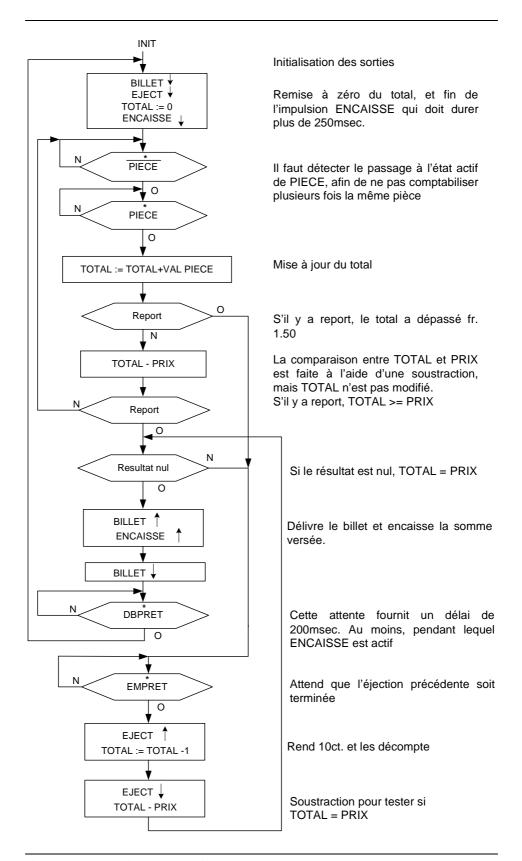

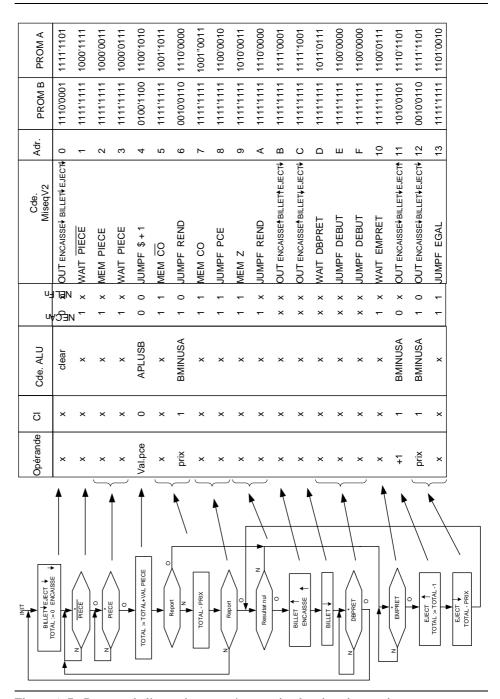

Pour illustrer la méthode de conception et les techniques de réalisation apparaissant dans ce chapitre, nous allons utiliser un second exemple: le développement d'un système digital gérant le fonctionnement d'un distributeur automatique de billets, donc les spécifications sont données ci-dessous. Cet exemple sera utilisé pour montrer l'évolution des unités de commande d'une version cablée à des structures micro-programmées.

#### Introduction.

La compagnie des Gyrobus Yverdonnois désire remplacer ses automates mécaniques de vente de billets par des machines à commande électronique. Nous sommes chargés de développer un prototype d'évaluation de la commande électronique, l'entreprise Bolomey S.A. est chargée de développer un collecteur de monnaie, un échangeur de monnaie et un distributeur de billets. Les spécifications de l'ensemble du système sont données ci-dessous.

# 4-1 Spécifications du distributeur

#### Spécifications préliminaires.

Le système de commande électronique doit diriger le fonctionnement du collecteur et de l'échangeur de monnaie, ainsi que du distributeur de billets, de façon à obtenir un système capable de vendre automatiquement des billets de Gyrobus à Fr. 0,90, et de rendre la monnaie si besoin est.

#### Fonctionnement désiré.

L'acheteur va introduire des pièces de monnaie dans le collecteur, pour un montant supérieur ou égal à 90 centimes. Lors de l'introduction de chaque pièce, notre commande doit en enregistrer la valeur et l'additionner au montant déjà payé, jusqu'à ce qu'il égal ou dépasse les 90 centimes, après quoi il faudra éjecter un billet et rendre la monnaie s'il y a lieu.

En cas de malfonctionnement, le client doit pouvoir récupérer l'argent versé, en appuyant sur un bouton poussoir, et remettre du même coup tout le système dans son état initial. Dans ce but, les pièces introduites sont d'abord conservées dans un godet intermédiaire du collecteur de monnaie. Par action mécanique directe, le bouton-poussoir vide ce godet intermédiaire dans le godet de retour.

Si tout se passe normalement, lorsque la monnaie a été rendue et le billet éjecté, la commande doit provoquer le vidage du godet intermédiaire dans la caisse, et se remettre dans l'état initial.

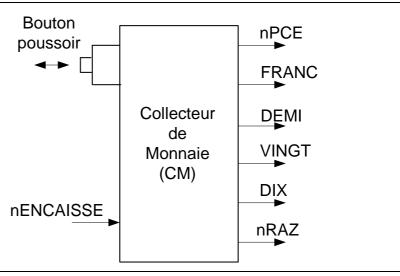

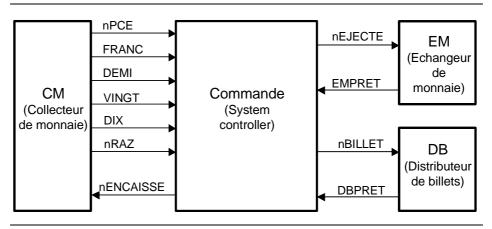

#### Collecteur de monnaie.

Le collecteur de monnaie a les caractéristiques suivantes:

- a) une seule fente d'introduction des pièces.

- b) grandeur de la fente limitant les pièces à 1Fr. maximum.

- c) les pièces de 1Fr., 50 ct., 20 ct., et 10 ct. suisses sont reconnues et acceptées par l'appareil.

- d) les fausses pièces ou les pièces endommagées sont automatiquement rejetées.

- e) un godet de collecte intermédiaire peut être vidé dans la caisse en actionnant un signal de commande appelé ENCAISSE, ou dans le godet de retour en agissant manuellement sur le bouton-poussoir prévu à cet effet.

Figure 4-1: Schéma bloc du collecteur de monnaie

Description des signaux:

nENCAISSE : entrée, provoque le vidage dans la caisse (magasin) des pièces collectées lors d'une transaction.

nPCE : sortie, indique qu'une pièce valide vient d'être introduite et que sa valeur a été déterminée.

FRANC, DEMI, VINGT, DIX : sorties, indiquant la valeur de la pièce qui vient d'être introduite.

nRAZ : sortie, active tant que l'on presse sur le bouton-poussoir.

Le chronogramme de la figure 4- 2 suivante définit les relations temporelles entre nPCE d'une part et FRANC, DEMI, VINGT ou DIX d'autre part.

Si une fausse pièce est détectée, plusieurs des signaux FRANC, DEMI, VINGT ou DIX peuvent être actifs, mais le signal nPCE reste inactif. Si une pièce valide est détectée, un seul des signaux FRANC, DEMI, VINGT, ou DIX sera actif lorsque nPCE est actif.

La commande impulsionnelle nENCAISSE doit durer plus de 250msec.

Figure 4-2: Relations temporelles entre différents signaux

## Échangeur de monnaie.

Les caractéristiques de l'échangeur de monnaie sont les suivantes:

- a) ce système électro-mécanique permet d'éjecter des pièces de 10ct dans le godet de retour.

- b) les pièces de 10 ct. sont prises dans un magasin de pièces spécialement prévu à cet effet.

- c) l'éjection est déclenchée par un signal d'entrée impulsionnel.

- d) un signal de sortie indique si l'échangeur est prêt à éjecter une nouvelle pièce.

- e) toute commande d'éjection faite pendant que l'échangeur n'est pas prêt est ignorée.

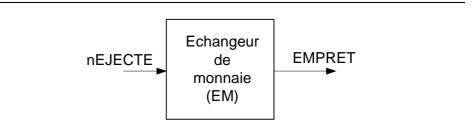

Figure 4-3 : Schéma bloc de l'échangeur de monnaie

#### Description des signaux

nEJECTE: entrée, provoque l'éjection d'une pièce de 10ct.

EMPRET : sortie, indique que l'échangeur est prêt à éjecter une nouvelle pièce.

Les relations temporelles entre ces signaux sont définies par le chrono-

#### gramme de la figure 4-4.

Figure 4-4: Relations temporelles entre les signaux nEJECT et EMPRET

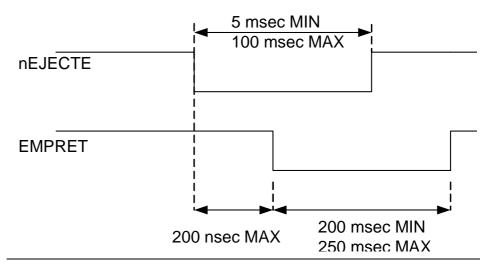

#### Mécanisme distributeur de billets.

Le mécanisme distributeur de billets a les caractéristiques suivantes:

- a) distribue un billet à la fois à l'aide d'un système électro-mécanique.

- b) comporte une entrée pour commander la distribution d'un billet.

- c) comporte une sortie indiquant si le distributeur est prêt à éjecter un nouveau billet ou non.

d)toute commande d'éjection d'un billet faite pendant que le distributeur n'est pas prêt est ignorée.

Figure 4-5: Schéma-bloc du mécanisme distributeur de billets

Description des signaux:

nBILLET: entrée, provoque l'éjection d'un billet, signal impulsionnel

DBPRE : sortie, indique que le distributeur est prêt à éjecter un nouveau billet.

Les relations temporelles entre les signaux nBILLET et DBPRET sont les mêmes que pour les signaux nEJECT et EMPRET.

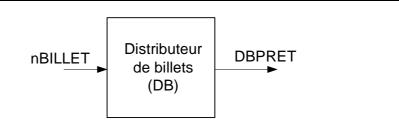

# 4-2 Schéma-bloc général et organigramme grossier

Les étapes 1 et 2 de la méthode de conception sont traitées (bien que de façon incomplète et en partie insatisfaisante, comme c'est souvent le cas) dans le paragraphe qui précède, pour notre exemple. Nous pouvons relever que plusieurs spécifications importantes, telles celles relatives à la fiabilité, à l'entretient, aux possibilités de modifications (adaptation du prix, par exemple), à l'environnement dans lequel l'appareil fonctionne (salle d'attente, plein air, couvert), etc, n'ont pas été définies. Par ailleurs, une surspécification, un à-priori restreignant inutilement notre liberté de concepteurs, s'est glissé dans la description du fonctionnement désiré. Mais nous y reviendrons par la suite.

En ce qui concerne les relations temporelles, nous n'avons pas de contraintes particulières si ce n'est que de respecter les caractéristiques des trois mécanismes utilisés. En effet, notre commande n'a pas besoin de fonctionner bien vite par rapport aux possibilités de l'électronique numérique, vu que les trois mécanismes ont des temps de réponse supérieur au dixième de seconde.

Nous pouvons donc passer à l'étape 3 et établir un schéma-bloc général. Celui-ci est représenté à la figure 4- 6.

Figure 4-6: Schéma-bloc général

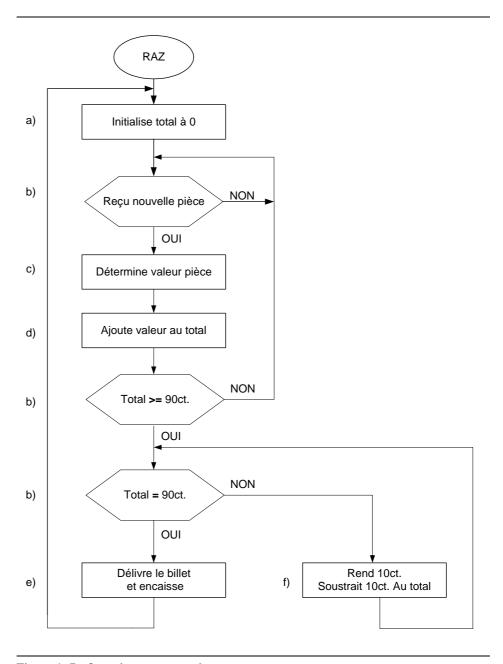

L'organigramme de la figure 4- 7 décrit un comportement globale possible de notre commande de distributeur de billets. Il s'agit ici d'une description grossière, que nous affinerons par la suite, mais on constate

immédiatement que le comportement envisagé est plus clairement décrit que par une suite de phrases.

Pour grossier qu'il soit, cet organigramme fait déjà apparaître quatre fonctions standard qui pourraient constituer l'ossature d'une unité de traitement.

- 1)l'addition de la valeur d'une pièce au total accumulé lors de cette transaction.

- 2) la mémorisation du total intermédiaire.

- 3)la comparaison entre le total et le prix.

- 4)la soustraction de 10ct. au total lorsqu'une pièce de 10ct. est rendue.

Figure 4-7: Organigramme grossier

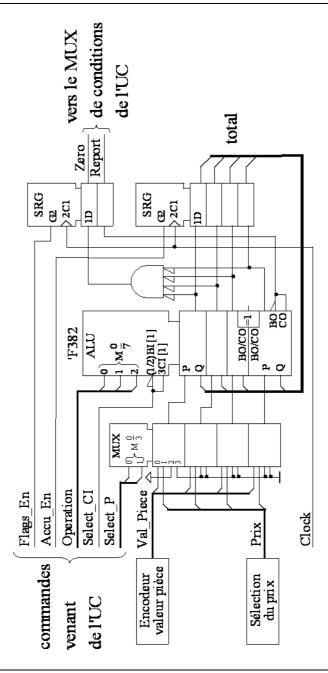

## 4-3 Partition commande / traitement

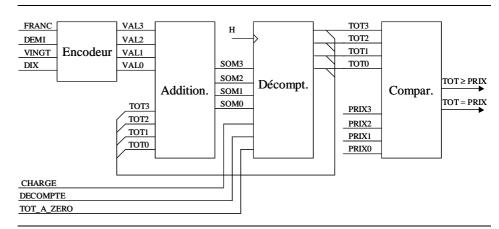

En utilisant les annotations visibles sur l'organigramme grossier (figure 4-7), nous allons identifier les fonctions à effectuer dans l'unité de traitement ou dans l'unité de commande.

- a)Pour initaliser le total à zéro, il faut effectuer une initilisation du registre contenant le total. Celui-ci sera situé dans l'UT.

- b) Le test de la réception d'une nouvelle pièce sera effectué dans l'UC. Cette dernière contrôle le séquencement du système.

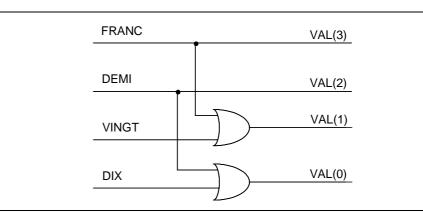

- c) Pour déterminer la valeur de la pièce, il faut transformer les signaux fournis par le collecteur de monnaie en une valeur utilisable par notre système, nombre en binaire (base 2). Nous allons utiliser un encodeur.

- d) Pour ajouter la valeur de la piéce au total, il faut un additionneur ainsi qu'un registre. Ces deux éléments se trouvent dans l'UT.

- e) Pour délivrer le billet et encaisser la monnaie, il faut activer les signaux nBILLET et nENCAISSE. Avant d'activer nBILLET, il faut s'assurer que le distributeur de billets soit pret. Il faut donc tester le signal DBPRET.

- f) L'éjection de la pièce sera commandé par l'UC qui activera le signal nEJECTE après s'être assuré que l'ejecteur de monnaie soit prêt. Chque fois qu'une pièce est rendue, il faudra soustraire 1 du total. Nous allons utiliser un décompteur qui se trouvera dans l'UT.

Nous allons dès lors concevoir l'unité de traitement spécialisée pour notre vendeur de billets en choisissant tout d'abord de favoriser la vitesse de fonctionnement. Nous pouvons dès lors lister les éléments nécessaires:

- -un additionneur pour effectuer l'addition.

- -un registre pour mémoriser le total (ou un compteur chargeable).

- -un comparateur pour comparer le total avec le prix

- -un soustracteur pour décompter le total (ou un compteur-décompteur).

Le schéma bloc de la figure 4- 8 représente une des solutions possible. La soustraction et la mémorisation seront faites à l'aide d'un compteur-décompteur chargeable. Le total et la valeur des pièces seront exprimés en nombre équivalent de pièces de 10ct. (10ct. est l'unité de mesure).

Figure 4-8: Schéma-bloc de la soustraction et de la mémorisation

Étant donné qu'un seul des signaux FRANC, DEMI, VINGT ou DIX sera actif à un instant donné, l'encodeur peut être réalisé très simplement comme nous le montre la figure 4-9.

Figure 4-9: Encodeur

Bien que notre cahier des charges ne le spécifie pas, nous savons bien que le prix du billet aura tendance à augmenter. Nous allons donc prévoir l'adaptation du prix à l'aide de simples ponts enfichables(jumpers).

Le compteur sera chargé avec le résultat de l'addition à chaque fois qu'une nouvelle pièce est introduite. La décrémentation se fera lorsque une pièce de 10ct. est rendue. La remise à zéro du total doit se faire lorsque l'automate vide le godet intermédiaire dans la caisse (nENCAISSE), ou lorsque le client presse sur le bouton-poussoir (nRAZ), ou lors de la mise sous tension.

L'unité de traitement que nous avons conçue restre très perfectible. En effet, les spécifications initiales étaient incomplètes, mais aussi trop restrictives. Ainsi, plusieurs cas de fonctionnement marginal n'ont pas été pris en considération: que se passe-t-il si les pièces sont introduites trop rapidement?, ou , pendant que l'appareil rend la monnaie, si le client presse sur le bouton-poussoir lorsqu'il a déjà reçu une partie du change?, si le client in-

troduit une pièce de 1Fr. Après avoir déjà payé 80ct.?, etc. La description du fonctionnement désiré a été faite de façon tendancieuse: elle pré-suppose que les valeurs des pièces versées vont être additionnées ce qui devrait être laissé au libre choix du concepteur, une soustraction ou décrémentations pouvant aussi faire l'affaire. Finalement, le choix que nous avons fait de favoriser la vitesse de traitement ne se justifie guère dans un appareil dont le fonctionnement global est tributaire de sous-systèmes électro-mécaniques beaucoup plus lents que la commande que nous allons concevoir, quelle que soit la structure de cette dernière. Les diverses améliorations seront des sujets d'exercice.

Figure 4-10: Schéma de l'UT

Le schéma de la figure 4- 10 appelle quelques remarques:

- 1) Les câbles qui relient le système de commande du vendeur de billets aux divers sous-systèmes électro-mécaniques sont suseptibles de capter des parasites. Il est souvent nécesaire de filtrer les signaux entrant dans un sous système logique. Une méthode souvent utilisée consiste à faire passer le signal à travers un réseau RC et un tigger de Schmitt, comme le signal PIECE.

- 2) les signaux DECOMPTE et nEJECTE peuvent être identiques, d'un point de vue purement logique. En effet, il s'agit de décrémenter le total à chaque fois qu'une pièce de 10ct. est rendue. Mais le signal nEJECT passera par un câble et peut donc être perturbé par des parasites. Pour éviter que ces parasites ne provoquent des décomptages intempestifs, le signal DECOMPTE sera généré séparement du signal nEJECTE.

- 3) à part l'unité de traitement, le reste du système logique est constitué de l'unité de commande, d'un circuit d'horloge et d'un circuit d'initialisation qui va activer le signal nINIT lors de la mise sous tension, lorsque le client presse sur le bouton-poussoir du collecteur de monnaie, ou lorsque le réparateur presse sur le bouton d'initialisation que nous ne manquerons pas de prévoir.

- 4) les symboles CEI d'un additionneur et d'un comparateur sont suffisamment explicites. Relevons toutefois que ces circuits sont cascadables (les fonctions d'addition et de comparaison peuvent toutes deux être décomposées en cascade) et disposent donc d'entrées et de sorties prévues à cet effet: le report d'entrée CI et de sortie CO pour l'additionneur, les entrées "<", "=", et ">", et les sorties "P<Q", "P=Q" et "P>Q" pour le comparateur.

## 4-4 Exercices

- 1) Modifier l'unité de traitement de la figure 4- 10 de façon à ce que le vendeur de billets fonctionne correctement lorsqu'un client introduit une pièce de 1Fr. après avoir déjà mis 80ct. dans l'appareil. Adapter l'organigramme de la figure 4- 7 s'il y a lieu.

- 2) Au lieu d'additionner les valeurs des pièces introduites jusqu'à ce que le total égale ou dépasse le prix, on peut imaginer de partir du prix et de soustraire les valeurs des pièces introduites. Le reste à payer pourra aussi être constamment affiché afin que le client sache où il en est. Concevoir un nouvelle unité de traitement suivant cette optique, après avoir établi un organigramme grossier qui décrive ce comportement.

- 3) Adapter le schéma de la figure 4- 10 et l'organigramme de la figure 4- 7, de façon à supprimer le comparateur et à effectuer la comparaison dans l'unité de commande.

- 4)Modifier l'organigramme de la figure 4- 7 et le schéma de figure 4- 10, de façon à ce que la totalisation du montant payé se fasse par comptage, plutôt que par addition proprement dite.

- 5) En faisant la synthèse des résultats obtenus dans les exercices 1 à 4, concevoir une unité de traitement intégrable dans un PLD de 24 pattes au maximum.

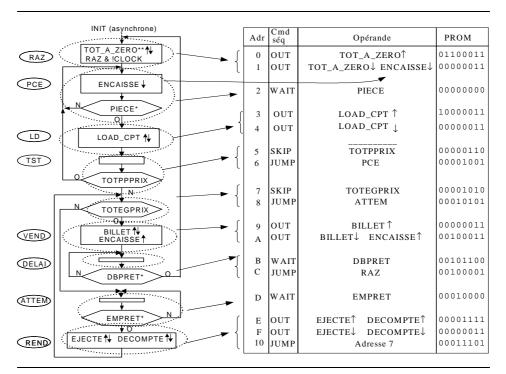

# 4-5 Organigramme détaillé

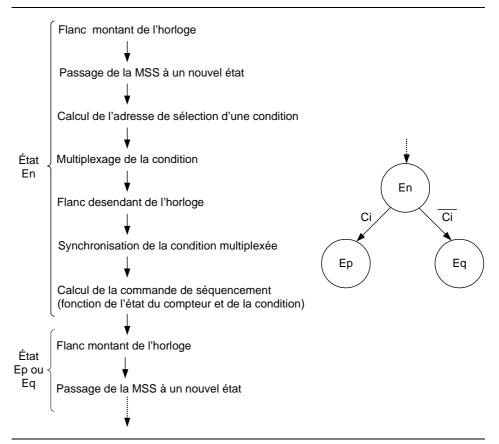

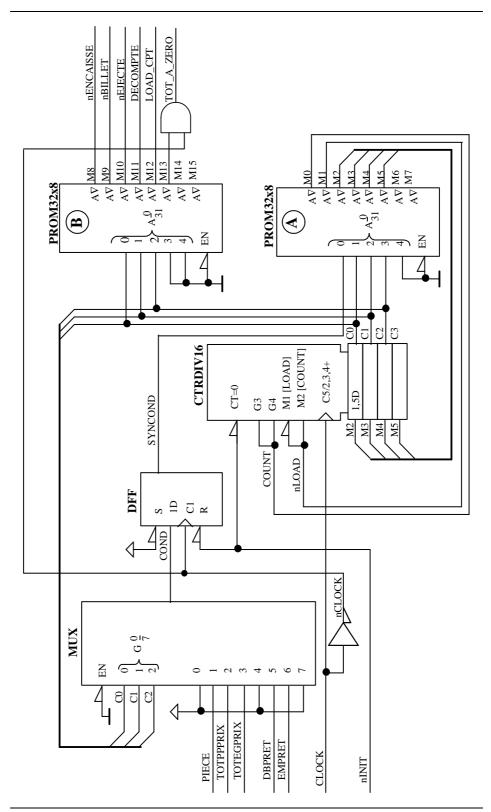

En tenant compte de l'unité de traitement de la figure 4- 10, nous pouvons maintenant établir un organigramme détaillé pour l'UC de notre automate de vente de billets, et le graphe correspondant.

Un organigramme détaillé doit comporter les commentaires utiles à sa compréhension (à coté des boîtes d'action ou de test), des noms pour les états (dans un cercle à côté de chaque boîte d'action inconditionnelles voire même les codes choisis pour les états ce qui facilitera l'utilisation de cet organigramme pour la documentation et le test.

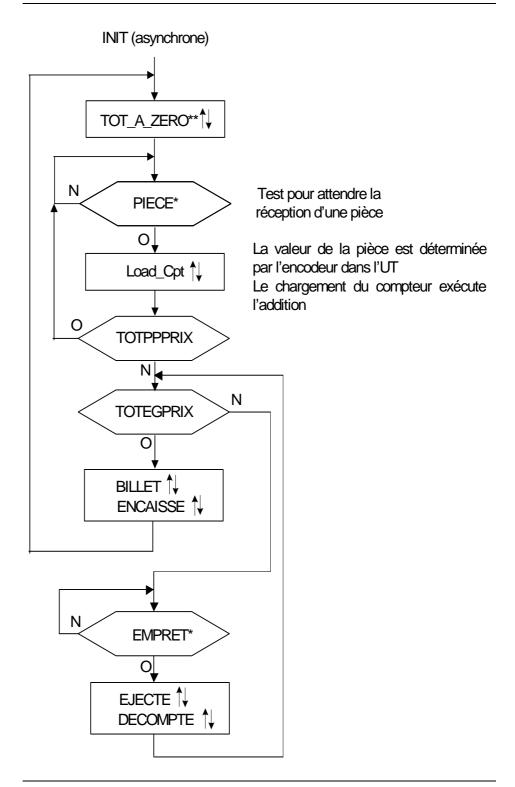

Pour établir un organigramme détaillé, il faut tenir compte de multiples facteurs: les entrées asynchrones, les contraintes temporelles, le découpage en état distincts, etc. Souvent, plusieurs étapes intermédiaires sont nécessaires avant d'aboutir à un organigramme détaillé satisfaisant. Ainsi, l'organigramme de la figure 4- 11 peut être considéré comme une première étape dans l'évolution de l'organigramme grossier de la figure 4- 7, vers l'organigramme détaillé de la figure VII33.

Figure 4- 11 : Organigramme détaillé de l'UC (premier raffinement)

L'organigramme de la figure 4- 11 a été établi à partir de celui de la figure 4- 7, en introduisant les noms des signaux que nous avons définis, en supprimant les opération réalisées par l'UT sans intervention de l'UC, et en tenant compte des caractéristiques de l'échangeur de monnaie.

Lors de l'activation du signal Load\_Cpt, le total ne sera pas à jour immédiatement. Il faudra tester l'état des signaux TOTEGPRIX et TOTPPPRIX dans un état suivant.

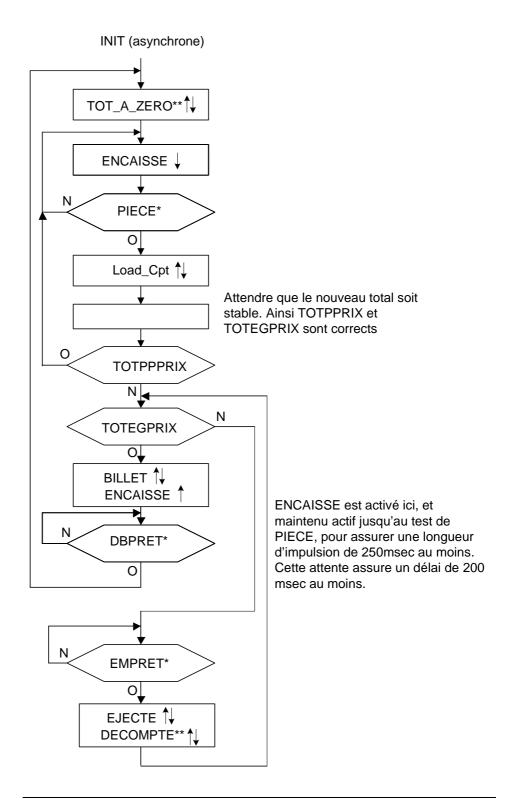

Il faut également nous assurer que toutes les sorties de l'UC respectent les contraintes temporelles de l'UT et du reste du système. Ainsi, l'impulsion à l'état actif de TOT\_A\_ZERO devra durer plus de 20ms, celle de BILLET et celle d'EJECTE doivent durer plus de 5msec mais moins de 100msec, celle d'nENCAISSE doit durer plus de 250msec, alors que quelques nanosecondes suffisent pour DECOMPTE (mais DECOMPTE et EJECTE peuvent être activées en même temps). Une période d'horloge située entre 5 et 100 msec. fera l'affaire pour TOT\_A\_ZERO, BILLET, EJECT et DECOMPTE. Pour ENCAISSE nous avons le choix entre créer un monostable à l'aide d'un compteur, ou maintenir le signal actif pendant le nombre de périodes voulu, en adaptant l'organigramme en conséquence. Nous choisirons cette deuxième solution, car elle est plus économique, mais nous utiliserons un test de DBPRET pour créer une attente d'au moins 200msec, à laquelle il suffira d'ajouter 50msec. Une seule période d'horloge suffira pour ajouter ces 50msec. si nous choisissons une fréquence d'horloge entre 10 et 20Hz.

Afin de pouvoir générer notre signal d'horloge à partir du réseau électrique, nous choisirons f = 50/4=12,5Hz (ou 67msec.).

L'organigramme de la figure 4- 12 tient compte de ces réflexions. Cet organigramme suppose que la fréquence d'horloge est de 10 à 20Hz.

Figure 4- 12 : Organigramme détaillé de l'UC (deuxième raffinement)

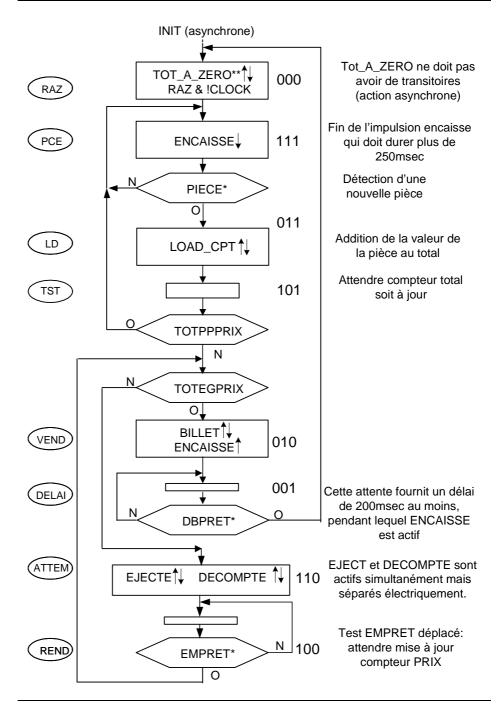

Si nous choisissons de réaliser une UC de type microprogrammée, l'organigramme de la figure 4- 12 peut être considérée comme suffisamment détaillé. Pour une UC de type câblé par contre, il va falloir étudier le découpage en états. En d'autres termes, il va falloir compléter et/ou modifier

l'organigramme de façon à ce que le graphe qui en sera tiré suivant les règles du paragraphe 3-4 réponde aux spécifications, comporte le moins d'états possible et tienne compte des entrées ou conditions asynchrones.

L'organigramme de la figure 4- 13 a été complété en vue de la réalisation d'une UC câblée. Nous voyons ainsi apparaître des boîtes d'action vides (puisqu'il n'y a aucune action à entreprendre) dans les boucles d'attente de DBPRET et de EMPRET: elles sont nécessaires pour respecter la règle n°1 du paragraphe 3-4, puisque chaque boucle doit comporter au moins un état. L'attente de PIECE, par contre, ne nécessite pas la création d'un état: il suffit d'attendre dans l'état où ENCAISSE est désactivé. Les tests de TOTPPPRIX et TOTEGPRIX doivent se faire après un état d'attente après le chargement du registre. En effet l'action de chargement a lieu en sortant de l'état. Il faut donc rajouter une boîte d'action entre le chargement du compteur et les tests de TOTPPPRIX et TOTEGPRIX.

Les tests de TOTPPPRIX et TOTEGPRIX peuvent se faire dans le même état, puisque ces deux entrées ne seront testées que lorsqu'on est sûr qu'elles sont stables (il n'est donc pas nécessaire de respecter la règle de codage n°5 retreinte).

Il ne reste plus qu'à donner des noms aux états, à mettre les commentaires utiles et à indiquer de quelle façon la sortie TOT\_A\_ZERO sera générée sans transitoires. Par la suite, les codes d'état peuvent être ajoutés à l'organigramme, afin de compléter la documentation (paragraphe 3-4).

Figure 4- 13 : Organigramme détaillé avec indiquations pour la réalisation de l'UC câblée.

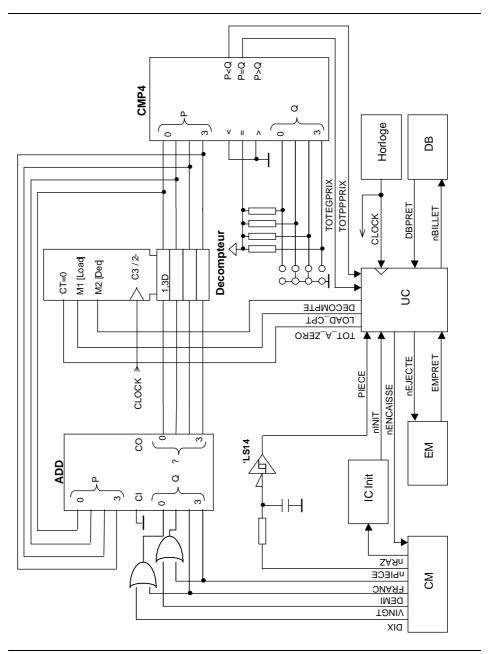

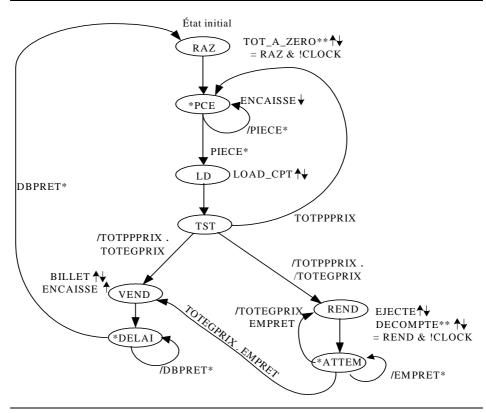

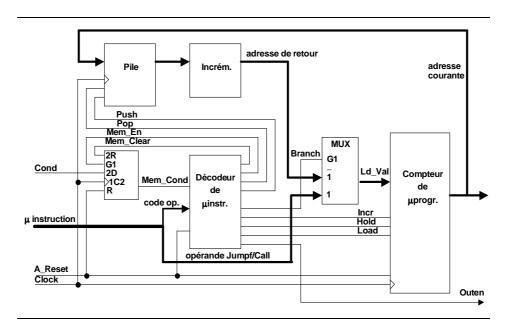

# 4-6 UC câblée

Nous allons établir un graphe à partir de l'organigramme détaillé de la figure figure 4-13, ce qui nous permettra de vérifier le découpage en états, puis nous procéderons comme pour la réalisation d'une MSS à l'aide d'un PLD. Le graphe obtenu est celui de la figure 4-14.

Figure 4-14: Graphe d'états

La sortie ENCAISSE pose un problème particulier, puisqu'elle doit être activée dans l'état VEND, désactivé dans l'état PCE, et ne doit pas être modifiée dans les autres états de la séquence. D'une façon générale, une telle sortie est générée à travers une bascule bistable (soit une bascule RS asynchrone, mais attention aux transitoires sur ses entrées, soit une bascule "edge-triggered" de type RS, JK ou D-CE), qui sera mise à 1 dans l'état VEND, et mise à 0 dans l'état PCE (ou l'inverse selon la polarité désirée). Notre problème accepte une solution plus simple, qui consiste à activer cette sortie dans les états VEND, DELAI et RAZ, et ne pas l'activer dans les autres états, car dans aucun état de notre séquence la sortie ENCAISSE ne dépend de ce qui s'est passé précédemment, rendant la mémorisation inutile.

Étant donné que nous avons des entrées asynchrones (en fait il faudrait plutôt dire "des entrées pouvant changer simultanément avec le flanc d'horloge qui détermine le passage de l'état où elles sont testées vers un état futur", mais c'est un peu long), nous devrons respecter la règle de codage n°5. La figure 4- 15 nous montre un codage possible.

|   | 00    | 01   | 11    | 10   |

|---|-------|------|-------|------|

| 0 | RAZ   | VEND | ATTEM | REND |

| 1 | DELAI | LD   | PCE   | TST  |

Figure 4- 15: Exemple d'un codage possible

Le développement de ce circuit en VHDL est documenté ce-après.

#### Description VHDL de l'UC câblée

```

entity UC is

port(

Clk_i : in std_logic;

Db_Pret_i : in std_logic;

Em_Pret_i : in std_logic;

Piece_i : in std_logic;

TotEgPrix_i : in std_logic;

TotPpPrix_i : in

std_logic;

nInit i

: in

std logic;

Decompte_o : out

std_logic;

Load_Cpt_o : out

std_logic;

Tot_A_Zero_o : out

std_logic;

nBillet_o : out std_logic;

nEject_o : out std_logic;

nEncaisse_o : out    std_logic

);

end entity UC ;

architecture FSM of UC is

type State_Type is (RAZ, PCE, LD, TST, ATTEM, REND,

VEND, DELAI);

signal Cur_State, Next_State : State_Type;

begin -- FSM

clocked : process( Clk_i, nReset_i)

-----

begin

if (nReset_i = '0') then

Cur_State <= RAZ;</pre>

elsif (Clk i'EVENT and Clk i = '1') then

Cur_State <= Next_State;</pre>

end if;

end process clocked;

```

```

_____

nextstate : process (Cur_State, TotPpPrix_i, Piece_i,

TotEgPrix_i, Em_Pret_i, Db_Pret_i)

begin

case Cur_State is

when RAZ =>

Next_State <= PCE;</pre>

when PCE =>

if (Piece_i = '0') then

Next_State <= PCE;</pre>

Next_State <= LD;</pre>

end if;

when LD =>

Next_State <= TST;</pre>

when TST =>

if (TotPpPrix_i = '1') then

Next_State <= PCE;</pre>

else

if (TotEgPrix_i = '1') then

Next_State <= VEND;</pre>

else

Next_State <= ATTEM;</pre>

end if;

end if;

when REND =>

if (TotEgPrix_i = '0') then

Next_State <= ATTEM;</pre>

else

Next_State <= VEND;</pre>

end if;

when ATTEM =>

if (Em_Pret_i = '0') then

Next_State <= ATTEM;</pre>

elsif (TotEgPrix_i = '1') then

Next_State <= VEND;</pre>

else

Next_State <= REND;</pre>

end if;

when VEND =>

Next_State <= DELAI;</pre>

when DELAI =>

if (Db_Pret_i = '0') then

Next_State <= DELAI;</pre>

else

Next_State <= RAZ;</pre>

end if;

when others =>

Next_State <= RAZ;</pre>

```

## 4-7 Exercices

- 6) Pour chacune des unités de traitement développées dans les excercices 1 à 5, établir l'organigramme détaillé et le graphe de l'UC câblée correspondante.

- 7)Réaliser l'UC câblée de la page 57 à l'aide d'une mémoire PROM et d'un registre parallèle-parallèle.