# PrimeCell<sup>®</sup> Generic Interrupt Controller (PL390)

Revision: r0p0

**Technical Reference Manual**

Copyright © 2008, 2009 ARM Limited. All rights reserved. ARM DDI 0416B (ID012510)

# PrimeCell Generic Interrupt Controller (PL390) Technical Reference Manual

Copyright © 2008, 2009 ARM Limited. All rights reserved.

#### **Release Information**

The Change history table lists the changes made to this book.

|                  |       |                  | Change history          |

|------------------|-------|------------------|-------------------------|

| Date             | Issue | Confidentiality  | Change                  |

| 28 April 2008    | А     | Non-Confidential | First release for r0p0  |

| 23 November 2009 | В     | Non-Confidential | Second release for r0p0 |

Change bistom

#### **Proprietary Notice**

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of ARM<sup>®</sup> Limited in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents PrimeCell Generic Interrupt Controller (PL390) Technical Reference Manual

|           |       | About this book                                      | X    |

|-----------|-------|------------------------------------------------------|------|

|           |       | Feedback                                             | xiii |

| Chapter 1 | Intro | oduction                                             |      |

| -         | 1.1   | About the GIC                                        | 1-2  |

|           | 1.2   | Compliance                                           | 1-5  |

|           | 1.3   | Features                                             | 1-6  |

|           | 1.4   | Interfaces                                           | 1-7  |

|           | 1.5   | Configurable options                                 | 1-8  |

|           | 1.6   | Test features                                        | 1-9  |

|           | 1.7   | Product documentation, design flow, and architecture | 1-10 |

|           | 1.8   | Product revisions                                    | 1-12 |

| Chapter 2 | Fund  | ctional Overview                                     |      |

| I.        | 2.1   | Functional interfaces                                | 2-2  |

|           | 2.2   | Implementation-defined behavior                      |      |

| Chapter 3 | Proc  | grammers Model                                       |      |

| •         | 3.1   | About the programmers model                          | 3-2  |

|           | 3.2   | Distributor register descriptions                    |      |

|           | 3.3   | CPU Interface register descriptions                  |      |

|           | 3.4   | Additional programming information                   |      |

| Chapter 4 | Proc  | grammers Model for Test                              |      |

| •         | 4.1   | About the programmers model for test                 | 4-2  |

|           |       |                                                      |      |

|            | 4.2<br>4.3 | Distributor integration test registers<br>CPU Interface integration test registers |      |

|------------|------------|------------------------------------------------------------------------------------|------|

| Appendix A | Sign       | al Descriptions                                                                    |      |

|            | A.1        | Clock and reset signals                                                            | A-2  |

|            | A.2        | AXI slave interface signals                                                        |      |

|            | A.3        | AHB-Lite signals                                                                   |      |

|            | A.4        | Interrupt signals                                                                  | A-10 |

|            | A.5        | Miscellaneous signals                                                              | A-11 |

| Appendix B | Inter      | rupt Signaling                                                                     |      |

| ••         | B.1        | Signaling interrupts when the GIC supports a single security state                 | B-2  |

|            | B.2        | Signaling interrupts when the GIC supports the Security Extensions                 |      |

| Appendix C | Revi       | sions                                                                              |      |

|            |            |                                                                                    |      |

Glossary

# List of Tables **PrimeCell Generic Interrupt Controller (PL390) Technical Reference Manual**

|            | Change history                                               | İİ    |

|------------|--------------------------------------------------------------|-------|

| Table 2-1  | Attribute formats                                            | . 2-4 |

| Table 3-1  | Distributor register summary                                 | . 3-5 |

| Table 3-2  | ic_type Register bit assignments                             | . 3-7 |

| Table 3-3  | dist_ident Register bit assignments                          | . 3-8 |

| Table 3-4  | ppi_if <n> Register bit assignments</n>                      | 3-21  |

| Table 3-5  | spi Register bit assignments                                 | 3-22  |

| Table 3-6  | periph_id_[3:0] Register bit assignments                     | 3-23  |

| Table 3-7  | periph_id_0 Register bit assignments                         | 3-23  |

| Table 3-8  | periph_id_1 Register bit assignments                         | 3-24  |

| Table 3-9  | periph_id_2 Register bit assignments                         | 3-24  |

| Table 3-10 | periph_id_3 Register bit assignments                         | 3-24  |

| Table 3-11 | periph_id_[7:4] Register bit assignments                     | 3-25  |

| Table 3-12 | periph_id_4 Register bit assignments                         | 3-26  |

| Table 3-13 | periph_id_5 Register bit assignments                         | 3-26  |

| Table 3-14 | periph_id_6 Register bit assignments                         | 3-27  |

| Table 3-15 | periph_id_7 Register bit assignments                         | 3-27  |

| Table 3-16 | periph_id_8 Register bit assignments                         | 3-28  |

| Table 3-17 | component_id Register bit assignments                        | 3-29  |

| Table 3-18 | CPU Interface register summary                               | 3-30  |

| Table 3-19 | cpu_if_ident Register bit assignments                        | 3-31  |

| Table 4-1  | Distributor test register summary                            | . 4-3 |

| Table 4-2  | legacy_int <n> Register bit assignments</n>                  |       |

| Table 4-3  | match_d <n> Register bit assignments</n>                     |       |

| Table 4-4  | enable_d <n> Register bit assignments in the Distributor</n> | . 4-6 |

| Table 4-5  | CPU Interface test register summary                          |       |

| Table 4-6  | integ_en_c <n> Register bit assignments</n>                  | . 4-7 |

| Table 4-7  | interrupt_out <n> Register bit assignments</n>               | 4-8  |

|------------|--------------------------------------------------------------|------|

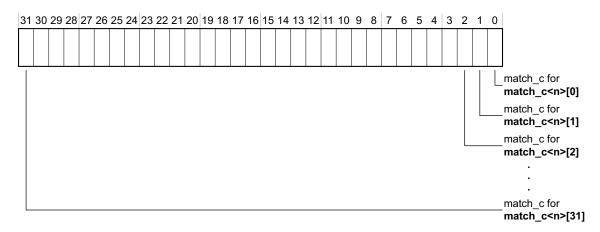

| Table 4-8  | match c <n> Register bit assignments in a CPU Interface</n>  | 4-9  |

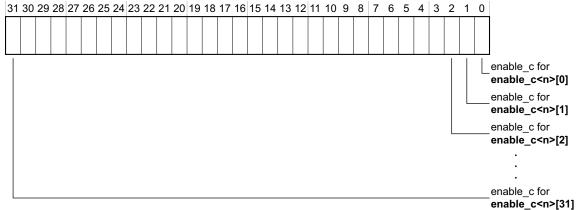

| Table 4-9  | enable_c <n> Register bit assignments in a CPU Interface</n> |      |

| Table A-1  | Clock and reset signals                                      | A-2  |

| Table A-2  | AXI-AW signals for the Distributor                           |      |

| Table A-3  | AXI-AW signals for a CPU Interface                           |      |

| Table A-4  | AXI-W signals for the Distributor                            | A-4  |

| Table A-5  | AXI-W signals for a CPU Interface                            | A-4  |

| Table A-6  | AXI-B signals for the Distributor                            |      |

| Table A-7  | AXI-B signals for a CPU Interface                            | A-5  |

| Table A-8  | AXI-AR signals for the Distributor                           | A-5  |

| Table A-9  | AXI-AR signals for a CPU Interface                           | A-6  |

| Table A-10 | AXI-R signals for the Distributor                            | A-6  |

| Table A-11 | AXI-R signals for a CPU Interface                            | A-7  |

| Table A-12 | AHB-Lite slave interface signals for the Distributor         | A-8  |

| Table A-13 | AHB-Lite slave interface signals for the CPU Interface       | A-9  |

| Table A-14 | Interrupt signals                                            | A-10 |

| Table A-15 | cfgsdisable signal                                           | A-11 |

| Table A-16 | enable_d <n> and match_d<n> signals</n></n>                  |      |

| Table A-17 | enable_c <n> and match_c<n> signals</n></n>                  | A-12 |

| Table C-1  | Differences between issue A and issue B                      | C-1  |

# List of Figures **PrimeCell Generic Interrupt Controller (PL390) Technical Reference Manual**

|             | Key to timing diagram conventions                 | xi   |

|-------------|---------------------------------------------------|------|

| Figure 1-1  | Interfaces on the GIC                             | 1-2  |

| Figure 1-2  | Example multiprocessor system                     | 1-3  |

| Figure 1-3  | Example uniprocessor system                       | 1-4  |

| Figure 2-1  | GIC block diagram                                 | 2-2  |

| Figure 2-2  | AXI slave interface                               | 2-3  |

| Figure 2-3  | AHB-Lite slave interface                          | 2-4  |

| Figure 2-4  | Distributor                                       | 2-5  |

| Figure 2-5  | Interrupt manipulation logic                      | 2-6  |

| Figure 2-6  | CPU Interface                                     | 2-6  |

| Figure 3-1  | Distributor register map                          | 3-3  |

| Figure 3-2  | CPU Interface register map                        | 3-4  |

| Figure 3-3  | ic_type Register bit assignments                  | 3-6  |

| Figure 3-4  | dist_ident Register bit assignments               | 3-8  |

| Figure 3-5  | Interrupt Security Register address map           | 3-9  |

| Figure 3-6  | Enable Set Register address map                   | 3-10 |

| Figure 3-7  | Enable Clear Register address map                 | 3-11 |

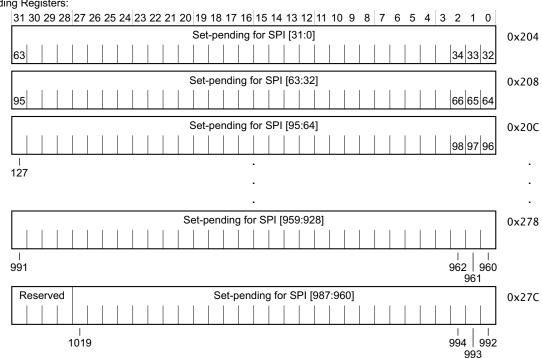

| Figure 3-8  | Pending Set Register address map                  | 3-13 |

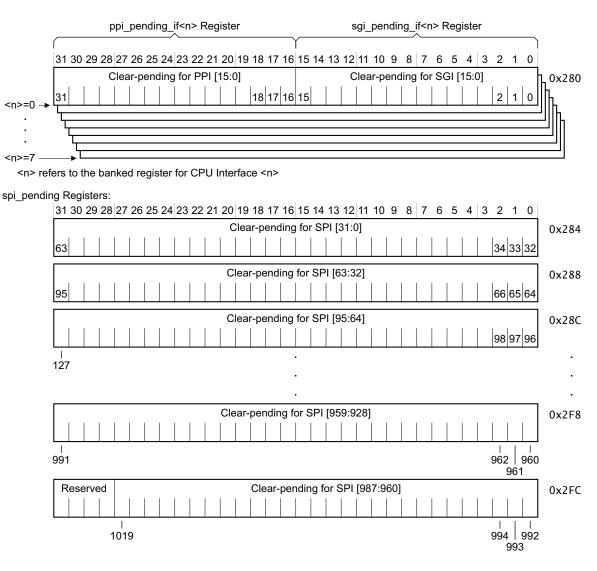

| Figure 3-9  | Pending Clear Register address map                | 3-14 |

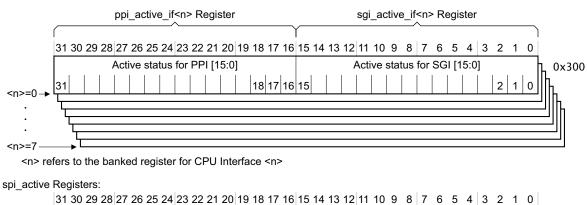

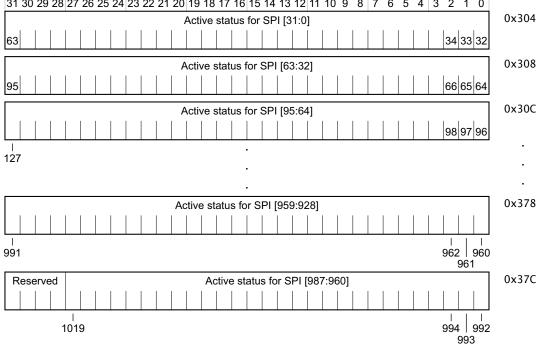

| Figure 3-10 | Active Status Register address map                | 3-15 |

| Figure 3-11 | Priority Level Register address map               | 3-17 |

| Figure 3-12 | targets_spi_ <intid> Register address map</intid> | 3-18 |

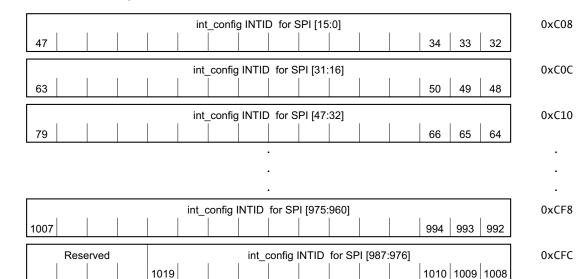

| Figure 3-13 | spi_config Register address map                   | 3-19 |

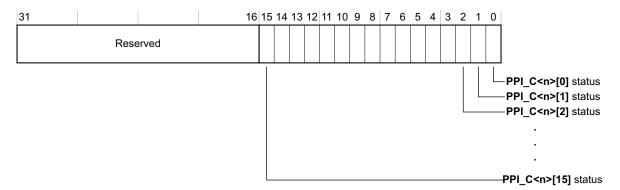

| Figure 3-14 | ppi_if <n> Register bit assignments</n>           | 3-20 |

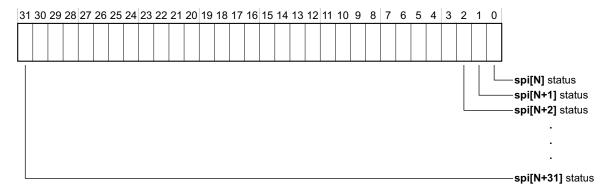

| Figure 3-15 | spi Register bit assignments                      | 3-21 |

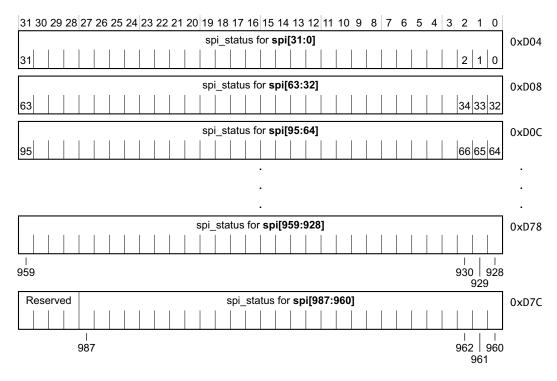

| Figure 3-16 | spi Register address map                          | 3-22 |

| Figure 3-17 | periph_id_[3:0] Register bit assignments          | 3-23 |

| Figure 3-18 | periph_id_[7:4] Register bit assignments                                           | 3-25 |

|-------------|------------------------------------------------------------------------------------|------|

| Figure 3-19 | periph_id_8 Register bit assignments                                               |      |

| Figure 3-20 | PrimeCell ID Register bit assignments                                              |      |

| Figure 3-21 | cpu_if_ident Register bit assignments                                              |      |

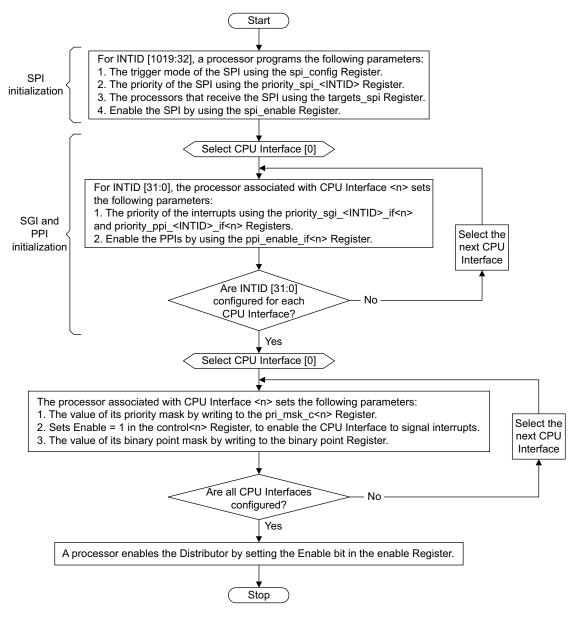

| Figure 3-22 | Initialization process for GICs that support a single security state               | 3-33 |

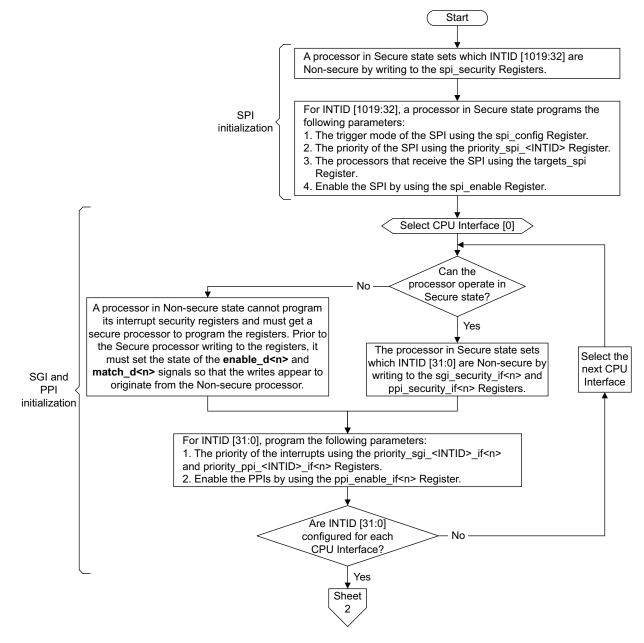

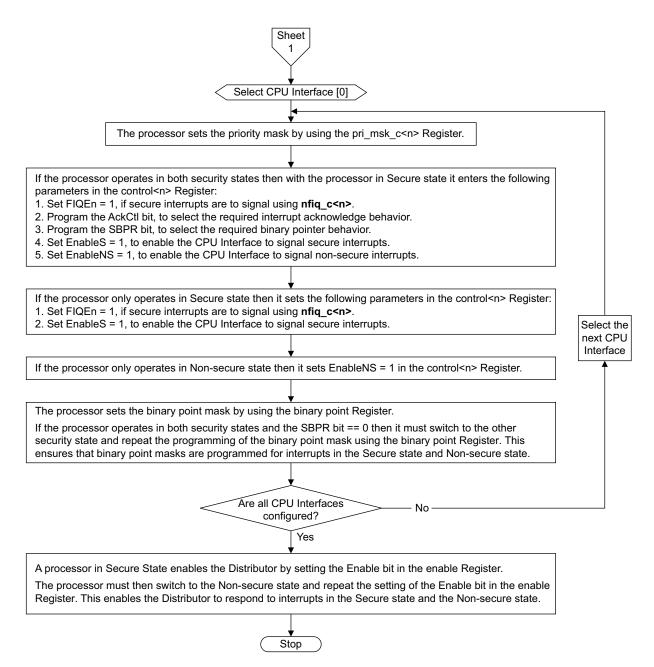

| Figure 3-23 | Initialization process for GICs that support the Security Extensions, sheet 1 of 2 | 3-34 |

| Figure 3-24 | Initialization process for GICs that support the Security Extensions, sheet 2 of 2 | 3-35 |

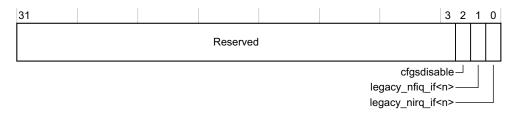

| Figure 4-1  | legacy_int <n> Register bit assignments</n>                                        | 4-4  |

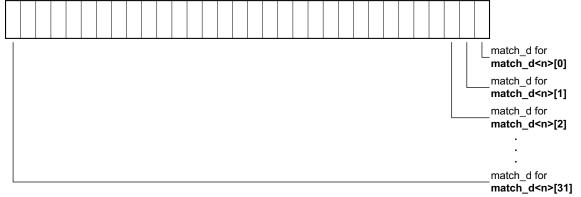

| Figure 4-2  | match_d <n> Register bit assignments</n>                                           | 4-5  |

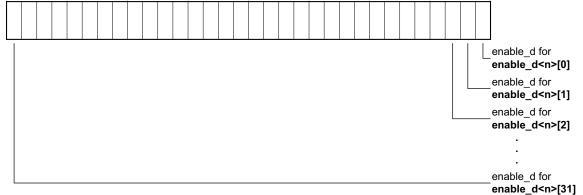

| Figure 4-3  | enable_d <n> Register bit assignments in the Distributor</n>                       | 4-6  |

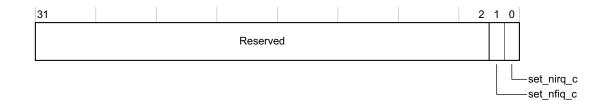

| Figure 4-4  | integ_en_c <n> Register bit assignments</n>                                        | 4-7  |

| Figure 4-5  | interrupt_out <n> Register bit assignments</n>                                     |      |

| Figure 4-6  | match_c <n> Register bit assignments in a CPU Interface</n>                        |      |

| Figure 4-7  | enable_c <n> Register bit assignments in a CPU Interface</n>                       | 4-10 |

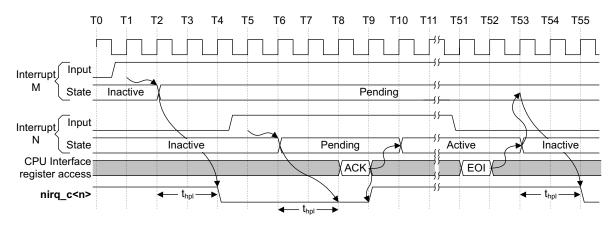

| Figure B-1  | Interrupt signaling using nirq_c                                                   | B-2  |

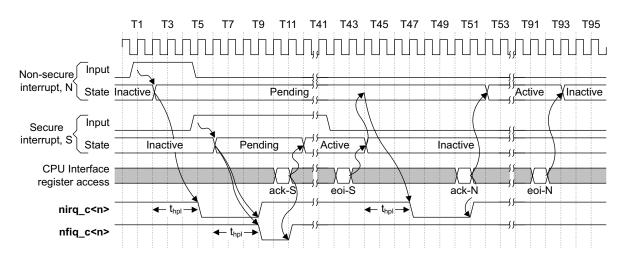

| Figure B-2  | Interrupt signaling using nirq_c and nfiq_c                                        | B-4  |

# Preface

This preface introduces the *PrimeCell Generic Interrupt Controller (PL390) Technical Reference Manual* (TRM). It contains the following sections:

- *About this book* on page x

- *Feedback* on page xiii.

# About this book

This is the TRM for the *PrimeCell Generic Interrupt Controller (PL390)*. The *Generic Interrupt Controller* (GIC) is a configurable interrupt controller that supports uniprocessor or multiprocessor systems.

| Product revision state | us           |                                                                                                                                            |

|------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                        | The rnpn id  | entifier indicates the revision status of the product described in this book, where:                                                       |

|                        | r <i>n</i>   | Identifies the major revision of the product.                                                                                              |

|                        | р <i>п</i>   | Identifies the minor revision or modification status of the product.                                                                       |

| Intended audience      |              |                                                                                                                                            |

|                        |              | s written for system designers, system integrators, and programmers who are r programming a <i>System-on-Chip</i> (SoC) that uses the GIC. |

| Using this book        |              |                                                                                                                                            |

|                        | This book is | s organized into the following chapters:                                                                                                   |

|                        | Chapter 1    | Introduction                                                                                                                               |

|                        |              | Read this for an introduction to the GIC and its features.                                                                                 |

|                        | Chapter 2    | Functional Overview                                                                                                                        |

|                        |              | Read this for a description of the major interfaces and the Implementation-defined behavior of the GIC.                                    |

|                        | Chapter 3    | Programmers Model                                                                                                                          |

|                        |              | Read this for a description of the memory map and registers.                                                                               |

|                        | Chapter 4    | Programmers Model for Test                                                                                                                 |

|                        |              | Read this for a description of the test registers.                                                                                         |

|                        | Appendix A   | A Signal Descriptions                                                                                                                      |

|                        |              | Read this for a description of the input and output signals.                                                                               |

|                        | Appendix l   | B Interrupt Signaling                                                                                                                      |

|                        |              | Read this for a description of how the GIC signals interrupts to a processor.                                                              |

|                        | Appendix (   | C Revisions                                                                                                                                |

|                        |              | Read this for a description of the technical changes between released issues of this book.                                                 |

|                        | Glossary     | Read this for definitions of terms used in this book.                                                                                      |

| Conventions            |              |                                                                                                                                            |

|                        | Convention   | s that this book can use are described in:                                                                                                 |

|                        |              | <i>graphical</i> on page xi                                                                                                                |

|                        | • Timin      | g diagrams on page xi                                                                                                                      |

• Signals on page xi.

# Typographical

The typographical conventions are:

| Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Highlights interface elements, such as menu names. Denotes signal names. Also used for terms in descriptive lists, where appropriate.                                |

| Denotes text that you can enter at the keyboard, such as commands, file<br>and program names, and source code.                                                       |

| Denotes a permitted abbreviation for a command or option. You can enter<br>the underlined text instead of the full command or option name.                           |

| Denotes arguments to monospace text where the argument is to be<br>replaced by a specific value.                                                                     |

| Denotes language keywords when used outside example code.                                                                                                            |

| Enclose replaceable terms for assembler syntax where they appear in code or code fragments. For example:<br>MRC p15, 0 <rd>, <crn>, <opcode_2></opcode_2></crn></rd> |

|                                                                                                                                                                      |

# **Timing diagrams**

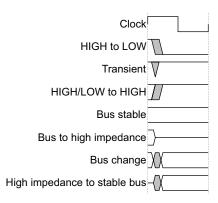

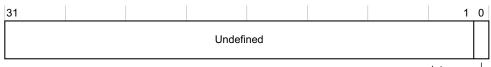

The figure named *Key to timing diagram conventions* explains the components used in timing diagrams. Variations, when they occur, have clear labels. You must not assume any timing information that is not explicit in the diagrams.

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

# Key to timing diagram conventions

# Signals

The signal conventions are:

| Signal level | The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means: |

|--------------|-------------------------------------------------------------------------------------------------------------|

|              | • HIGH for active-HIGH signals                                                                              |

|              | • LOW for active-LOW signals.                                                                               |

|              |                                                                                                             |

Lower-case n At the start or end of a signal name denotes an active-LOW signal.

# Additional reading

This section lists publications by ARM and by third parties.

See Infocenter, http://infocenter.arm.com, for access to ARM documentation.

### **ARM** publications

This book contains information that is specific to this product. See the following documents for other relevant information:

- PrimeCell Generic Interrupt Controller (PL390) Implementation Guide (ARM DII 0178)

- PrimeCell Generic Interrupt Controller (PL390) Integration Manual (ARM DII 0179)

- PrimeCell Generic Interrupt Controller (PL390) Supplement to AMBA<sup>®</sup> Designer (FD001) User Guide (ARM DSU 0008)

- AMBA Designer (FD001) User Guide (ARM DUI 0333)

- ARM Generic Interrupt Controller Architecture Specification (ARM IHI 0048)

- ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406)

- AMBA AXI Protocol v1.0 Specification (ARM IHI 0022)

- AMBA 3 AHB-Lite Protocol v1.0 Specification (ARM IHI 0033).

### Other publications

This section lists relevant documents published by third parties:

• JEDEC Standard Manufacturer's Identification Code, JEP106, http://www.jedec.org.

# Feedback

ARM welcomes feedback on this product and its documentation.

# Feedback on this product

If you have any comments or suggestions about this product, contact your supplier and give:

- The product name.

- The product revision or version.

- An explanation with as much information as you can provide. Include symptoms and diagnostic procedures if appropriate.

# Feedback on content

If you have comments on content then send an e-mail to errata@arm.com. Give:

- the title

- the number, ARM DDI 0416B

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# Chapter 1 Introduction

This chapter introduces the GIC (PL390). It contains the following sections:

- *About the GIC* on page 1-2

- *Compliance* on page 1-5

- *Features* on page 1-6

- *Interfaces* on page 1-7

- *Configurable options* on page 1-8

- *Test features* on page 1-9

- Product documentation, design flow, and architecture on page 1-10

- *Product revisions* on page 1-12.

# 1.1 About the GIC

The GIC is an *Advanced Microcontroller Bus Architecture* (AMBA) and ARM Architecture compliant *System-on-Chip* (SoC) peripheral. It is a high-performance, area-optimized interrupt controller with on-chip AMBA bus interfaces that, depending on the configuration, conform to the AMBA *Advanced eXtensible Interface* (AXI) protocol or the AMBA AHB-Lite protocol.

The main product configurations are:

### GIC with AHB-Lite slave interfaces

Implements the AHB-Lite protocol and contains a single CPU Interface.

#### GIC with AXI slave interfaces

Implements the AXI protocol, supports the Security Extensions, and contains up to eight CPU Interfaces.

You can configure the GIC to provide the optimum features, performance, and gate count required for your intended application. For a summary of the configurable features supported, see *Configurable options* on page 1-8.

The GIC implements the ARM Generic Interrupt Controller Architecture. See the *ARM Generic Interrupt Controller Architecture Specification* for information about the:

- architecture and interrupt types

- interrupt prioritization

- programmers model.

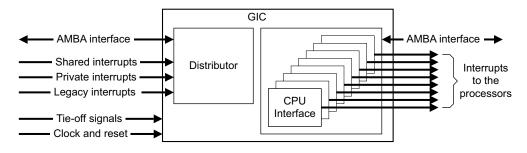

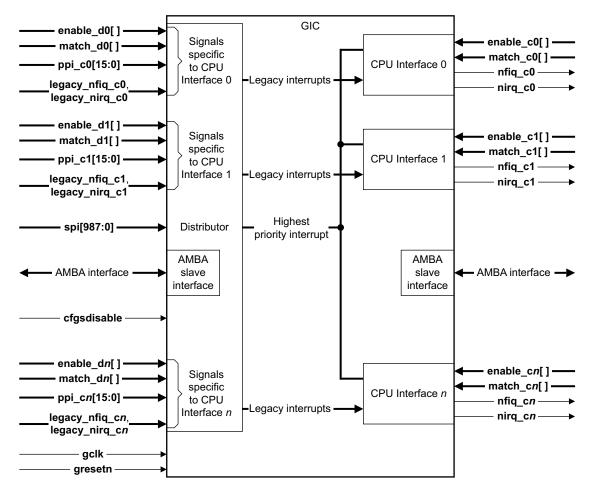

Figure 1-1 shows the interfaces that are available on the GIC.

# Figure 1-1 Interfaces on the GIC

In Figure 1-1, the configuration of the GIC determines:

• the number of CPU Interfaces

— Note — — —

if both AMBA interfaces are either AXI or AHB-Lite.

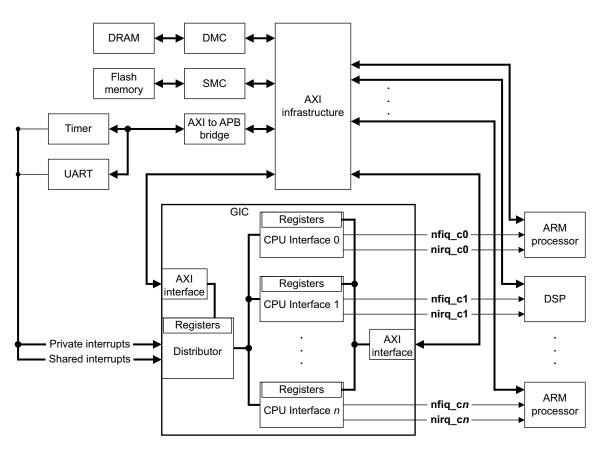

Figure 1-2 on page 1-3 shows the GIC in an example multiprocessor system.

Figure 1-2 Example multiprocessor system

The GIC example multiprocessor system contains:

- A GIC configured to use the AXI protocol. The GIC provides a CPU Interface for each bus master that connects to it.

- AXI bus masters:

- two ARM processors.

- a Digital Signal Processor (DSP).

- up to five additional bus masters. For clarity, these are not shown.

- AXI infrastructure component.

- PrimeCell slaves:

- a Dynamic Memory Controller (DMC)

- a Static Memory Controller (SMC)

- a Timer

- a Universal Asynchronous Receiver-Transmitter (UART).

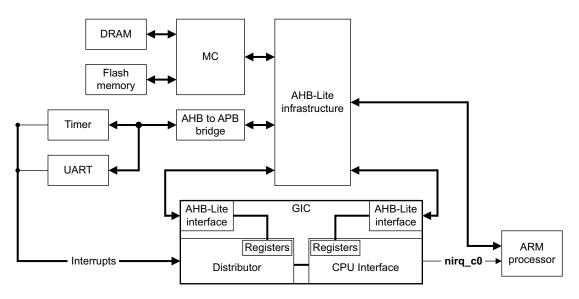

Figure 1-3 on page 1-4 shows the GIC in an example uniprocessor system.

Figure 1-3 Example uniprocessor system

The GIC example uniprocessor system contains:

- a GIC configured to use the AHB-Lite protocol

- an ARM processor

- AHB infrastructure component

- PrimeCell slaves:

- a *Memory Controller* (MC)

- a Timer

- a Universal Asynchronous Receiver-Transmitter (UART).

The AHB-Lite interconnect enables the processor to access the slaves. The Timer and UART connect to the AHB-Lite interconnect using an AHB to APB bridge component.

# 1.2 Compliance

The GIC is compliant with the following standards and protocols:

- AMBA 3 AXI protocol

- AMBA 3 AHB-Lite protocol

- ARM Generic Interrupt Controller Architecture.

# 1.3 Features

The GIC provides the following features:

- Support for three interrupt types:

- Software Generated Interrupt (SGI)

- Private Peripheral Interrupt (PPI)

- Shared Peripheral Interrupt (SPI).

- Programmable interrupts that enable you to set the:

- security state for an interrupt

- priority level of an interrupt

•

- enabling or disabling of an interrupt

- processors that receive an interrupt.

- Enhanced security features, when the GIC is configured to support the Security Extensions.

# 1.4 Interfaces

The GIC provides separate AMBA slave interfaces that enable you to program the Distributor and the CPU Interfaces. Depending on the configuration, the GIC contains either:

- two AMBA AXI slave interfaces

- two AMBA 3 AHB-Lite slave interfaces.

# 1.5 Configurable options

During implementation of the GIC, the features that are configurable depend on the configuration as follows:

# **Uniprocessor configurations**

• AMBA protocol, either AXI or AHB-Lite. When set to AXI then the GIC can be configured to support the Security Extensions.

# **Multiprocessor configurations**

- The width of the AXI ID tag signals.

- The number of CPU Interfaces.

- The number of lockable SPIs.

- The number of PPIs for a CPU Interface.

- PPIs can be pulse-sensitive or level-sensitive.

- To synchronize a PPI to **gclk**.

- To register a PPI.

- Security Extensions support, which enables the GIC to operate using the Secure state and the Non-secure state.

# All configurations

- The number of SGIs for each processor, from zero to 16.

- The number of SPIs, from one to 988.

- To synchronize an SPI to **gclk**.

- To register an SPI.

- The number of priority levels.

- The number of register slices in the highest pending interrupt logic.

- To include legacy interrupts for all CPU Interfaces in the GIC. Each legacy interrupt can be:

- either pulse-sensitive or level-sensitive

- synchronized to gclk

- registered.

# 1.6 Test features

The GIC provides integration test logic, see Chapter 4 Programmers Model for Test.

# **1.7 Product documentation, design flow, and architecture**

This section describes the GIC books, how they relate to the design flow, and the relevant architectural standards and protocols.

See *Additional reading* on page xii for more information about the books described in this section.

# 1.7.1 Documentation

The GIC documentation is as follows:

# **Technical Reference Manual**

The *Technical Reference Manual* (TRM) describes the functionality and the effects of functional options on the behavior of the GIC. It is required at all stages of the design flow. Some behavior described in the TRM might not be relevant because of the way that the GIC is implemented and integrated. If you are programming the GIC then contact:

- the implementer to determine the build configuration of the implementation

- the integrator to determine the signal configuration of the SoC that you are using.

The TRM complements protocol specifications and relevant external standards. It does not duplicate information from these sources.

# User Guide

The User Guide (UG) describes:

- the available build configuration options and related issues in selecting them

- how to use AMBA Designer to:

- configure the GIC

- generate the *Register Transfer Level* (RTL).

The UG is a confidential book that is only available to licensees.

# **Implementation Guide**

The Implementation Guide (IG) describes the:

- Out-Of-Box instructions

- synthesis constraints.

The ARM product deliverables include reference scripts and information about using them to implement your design.

The IG is a confidential book that is only available to licensees.

# **Integration Manual**

The *Integration Manual* (IM) describes how to integrate the GIC into a SoC. It includes describing the signals that the integrator must tie off to configure the macrocell for the required integration. Some of the integration is affected by the configuration options used when implementing the GIC.

The IM is a confidential book that is only available to licensees.

# 1.7.2 Design flow

The GIC is delivered as synthesizable RTL. Before it can be used in a product, it must go through the following process:

- 1. Implementation. The implementer configures and synthesizes the RTL to produce a hard macrocell.

- 2. Integration. The integrator connects the implemented design into an SoC. This includes connecting it to a memory system and peripherals.

- 3. Programming. The system programmer develops the software required to control the GIC and tests the required application software.

Each stage of the process:

- can be performed by a different party

- can include options that affect the behavior and features at the next stage:

# **Build configuration**

The implementer chooses the options that affect how the RTL source files are pre-processed. They usually include or exclude logic that can affect the area or maximum frequency of the resulting macrocell.

# **Configuration inputs**

The integrator configures some features of the GIC by tying inputs to specific values. These configurations affect the start-up behavior prior to the software taking control. They can also limit the options available to the software. See *Miscellaneous signals* on page A-11.

# Software control

The programmer updates the GIC by programming particular values into software-visible registers. This affects the behavior of the GIC.

# 1.7.3 ARM architecture and protocol information

The GIC complies with, or implements, the specifications described in:

- ARM generic interrupt controller architecture

- Advanced Microcontroller Bus Architecture.

# ARM generic interrupt controller architecture

The GIC implements the ARM generic interrupt controller architecture. See the *ARM Generic Interrupt Controller Architecture Specification*.

# Advanced Microcontroller Bus Architecture

The GIC complies with the:

- AMBA 3 AXI protocol, see the AMBA AXI Protocol Specification

- AMBA 3 AHB-Lite protocol, see the AMBA 3 AHB-Lite Protocol v1.0 Specification.

# 1.8 Product revisions

This section describes the differences in functionality between the product revisions:

r0p0 First release.

# Chapter 2 Functional Overview

This chapter describes the GIC operation. It contains the following sections:

- *Functional interfaces* on page 2-2

- *Implementation-defined behavior* on page 2-9.

# 2.1 Functional interfaces

Figure 2-1 shows a block diagram of the GIC.

# Figure 2-1 GIC block diagram

Some configurations of the GIC might not include all of the signals that Figure 2-1 shows.

The main blocks of the GIC are:

• AMBA slave interfaces

– Note –

- *Distributor* on page 2-5

- *CPU Interface* on page 2-6

- Clock and reset on page 2-7

- *enable and match signals* on page 2-7.

# 2.1.1 AMBA slave interfaces

The AMBA slave interfaces provide access to the GIC registers that enable you to program the system configuration parameters and obtain status information. See Chapter 3 *Programmers Model* for more information.

The GIC provides two AMBA slave interfaces, one for the Distributor and one that the CPU Interfaces share. You can configure the AMBA slave interfaces to be either AXI or AHB-Lite and these are described in:

- AXI slave interface

- *AHB-Lite slave interface* on page 2-4.

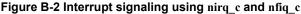

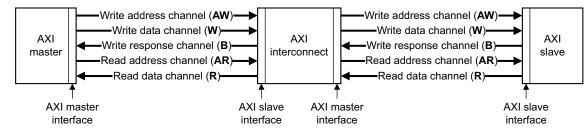

# AXI slave interface

Both AXI slave interfaces use a 32-bit data bus and consist of the following AXI channels:

- Write-Address (AW)

- Write-Data (W)

- Write response (B)

- Read-Address (AR)

- Read-Data (R).

For information about the AXI protocol see the AMBA AXI Protocol v1.0 Specification.

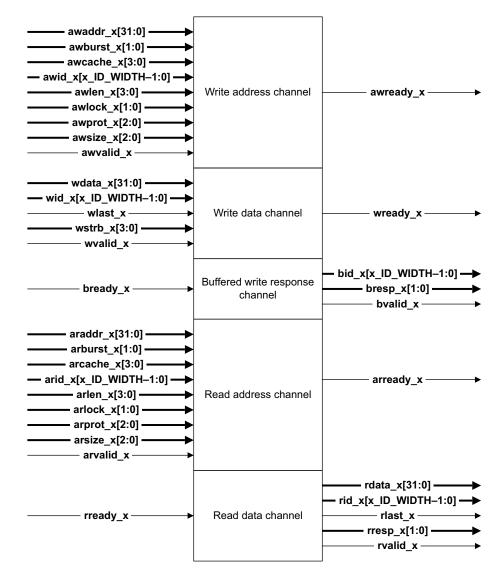

Figure 2-2 shows the AXI slave interface external signals.

Figure 2-2 AXI slave interface

\_\_\_\_\_Note \_\_\_\_\_

In Figure 2-2 on page 2-3:

- Each signal uses an \_x suffix to identify the AXI slave interface, where x is:

- d Distributor

- **c** CPU Interface(s).

- **x\_ID\_WIDTH** is the width of the ID tag, see *AXI slave interface signals* on page A-3.

- The clock and reset signals are not shown, see *Clock and reset signals* on page A-2.

Table 2-1 shows the AXI slave interface attributes and their values.

#### **Table 2-1 Attribute formats**

| Attribute <sup>a</sup>         | Value |

|--------------------------------|-------|

| Combined acceptance capability | 1     |

| Write interleave depth         | 1     |

| Read data reordering depth     | 1     |

a. See *Glossary* for a description of these AXI attributes.

#### AHB-Lite slave interface

When a GIC is configured to support the AHB-Lite protocol, then both AHB-Lite slave interfaces use a 32-bit data bus and are fully-compliant AHB-Lite slaves. For information about the AHB-Lite protocol see the *AMBA 3 AHB-Lite Protocol v1.0 Specification*.

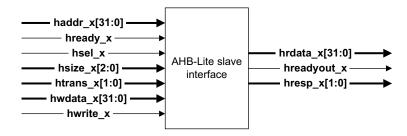

Figure 2-3 shows the AHB-Lite external signals.

#### Figure 2-3 AHB-Lite slave interface

—— Note – In Figure 2-3:

- Each signal uses an x suffix to identify the AHB-Lite interface, where x is:

- d Distributor

- c CPU Interface.

- The clock and reset signals are not shown, see *Clock and reset signals* on page A-2.

# 2.1.2 Distributor

The Distributor receives interrupts and provides the highest priority interrupt to the corresponding CPU Interface. An interrupt with a lower priority is forwarded to the appropriate CPU Interfaces when it becomes the highest priority pending interrupt.

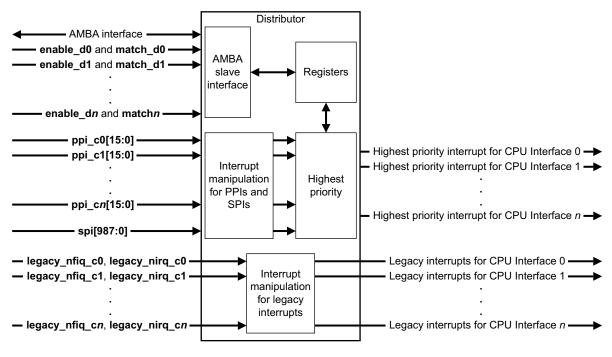

Figure 2-4 shows the Distributor.

#### Figure 2-4 Distributor

In multiprocessor configurations, the Distributor provides up to 16 *Private Peripheral Interrupts* (PPIs) for each CPU Interface. The Distributor only enables these interrupts to be forwarded to the corresponding CPU Interface.

The Distributor provides from 1 to 988 *Shared Peripheral Interrupts* (SPIs). For each SPI, you can program the Distributor to control how many CPU Interfaces it routes the interrupt to.

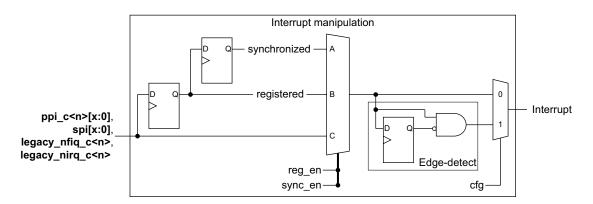

#### Interrupt manipulation block

The interrupt manipulation block enables the Distributor to manipulate an external interrupt as follows:

- the first stage provides the option of registering or synchronizing the interrupt

- the second stage provides an edge-detect option. This option is selected when the interrupt is set to be pulse-sensitive.

Figure 2-5 on page 2-6 shows the interrupt manipulation logic.

#### Figure 2-5 Interrupt manipulation logic

When you configure an external interrupt to be synchronized then the interrupt incurs an additional latency of two **gclk** cycles.

—Note —

The GIC enables you to configure the synchronization of any combination of PPIs, SPIs, and legacy interrupts.

When you configure a legacy interrupt or PPI, or program an SPI, to be pulse-sensitive then the GIC controls the 2-input multiplexor, in Figure 2-5, so that it selects the signal that passes through the edge-detect logic. The Distributor recognizes a pulse when the input is observed LOW and then HIGH on two consecutive rising edges of **gclk**. A pulse interrupt must be asserted for at least one **gclk** cycle to enable the Distributor to observe it.

```

— Note —

```

When configuring the legacy interrupts for CPU Interface *n*, you must set them to be level-sensitive if CPU Interface *n* connects to an ARM processor.

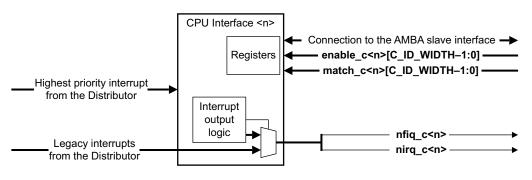

# 2.1.3 CPU Interface

A CPU Interface contains a programmable interrupt priority mask and it only accepts Pending interrupts if the priority of the interrupt is higher than the:

- programmed interrupt priority mask

- interrupts that the processor is currently servicing.

Figure 2-6 shows a CPU Interface.

#### Figure 2-6 CPU Interface

# 2.1.4 Clock and reset

This section describes:

- Clock

- Reset.

# Clock

All configurations of the GIC use a single clock input, **gclk**. See *Clock and reset signals* on page A-2.

# Reset

The GIC provides a single reset input, gresetn. See Clock and reset signals on page A-2.

# 2.1.5 enable and match signals

When the GIC contains two or more CPU Interfaces then it provides the following signals:

- enable\_d<n>[D\_ID\_WIDTH-1:0]

- match d<n>[D ID WIDTH-1:0]

- enable c<n>[C ID WIDTH-1:0]

- match c<n>[C ID WIDTH-1:0].

Where:

| <n></n>    | Is a number, from 0 to 7, that identifies a CPU Interface                                           |

|------------|-----------------------------------------------------------------------------------------------------|

| D_ID_WIDTH | Is the width of the AXI ID signals on the Distributor interface.                                    |

| C_ID_WIDTH | Is the width of the AXI ID signals on the AMBA interface that enables access to the CPU Interfaces. |

The **enable** signals function as a mask select on the AXI ID signals and the result is compared with the **match** signals. If the comparison is true then the GIC provides access to the registers for the relevant CPU Interface, otherwise the GIC ignores writes and reads return zero.

For the Distributor, it provides access to the banked registers for a CPU Interface when:

- (arid\_d & enable\_d<n>) == match\_d<n>

- (awid\_d & enable\_d<n>) == match\_d<n>

— Note —

When an access to a non-banked register in the Distributor occurs then it provides access to the register irrespective of the state of the **enable\_d** and **match\_d** signals.

The GIC provides access to a CPU Interface and its registers when:

- (arid\_c & enable\_c<n>) == match\_c<n>

- (awid\_c & enable\_c<n>) == match\_c<n>

— Note —

• By changing the state of the **match** and **enable** signals, a processor in Secure state can then access any of the banked registers for all other CPU Interfaces in the GIC. Similarly, a processor in Non-secure state can also modify the **match** and **enable** signals but the GIC only provides access to the banked registers, for all other CPU Interfaces, that are accessible in Non-secure state.

- You must ensure that only one set of **enable\_d<n>** and **match\_d<n>** signals are valid for an active AXI ID tag to the Distributor. If the value of the AXI ID tag enables the Distributor to select multiple banked registers then the behavior is Unpredictable.

- You must ensure that only one set of **enable\_c<n>** and **match\_c<n>** signals are valid for an active AXI ID tag to the AXI slave interface that accesses the CPU Interfaces. If the value of the AXI ID tag enables the GIC to select multiple banked registers then the behavior is Unpredictable.

# 2.2 Implementation-defined behavior

This section describes the behavior of the GIC which the *ARM Generic Interrupt Controller Architecture Specification* defines as being Implementation-defined. It contains the following sections:

- Number of CPU Interfaces

- Number of interrupt inputs

- Legacy interrupts

- *Programmable trigger-mode of PPIs* on page 2-10

- Lockable SPI (LSPI) support on page 2-10

- Number of priority levels on page 2-10

- Effect of updating the Priority Level Register for Active interrupts on page 2-10

- Interrupt prioritization of interrupts with equal priority on page 2-10

- Arbitration of SPIs which target multiple processors on page 2-11

- Initial value of the Interrupt Security Register on page 2-11

- Access restrictions of registers that are specific to a CPU Interface on page 2-11

- Minimum supported value in the Binary Point Register on page 2-11.

# 2.2.1 Number of CPU Interfaces

The number of CPU Interfaces is configurable from one to eight inclusive. The AMBA Designer documentation provides information about configuring the GIC, see *Additional reading* on page xii.

# 2.2.2 Number of interrupt inputs

The GIC provides the following types of interrupt:

- Software Generated Interrupt (SGI)

- Private Peripheral Interrupt (PPI)

- Shared Peripheral Interrupt (SPI).

# Software Generated Interrupt (SGI)

You can configure the GIC to provide up to 16 SGIs for each CPU Interface. Each interrupt is assigned an interrupt ID number, INTID[15:0].

# Private Peripheral Interrupt (PPI)

When you configure the GIC to contain more than one CPU Interface then the Distributor can provide from zero to 16 PPIs for each CPU Interface. The Distributor ensures that the interrupts it receives on the **ppi\_c<n>[15:0]** signals are only accessible to the relevant CPU Interface, that is, CPU Interface *n*.

# Shared Peripheral Interrupt (SPI)

You can configure the GIC to support up to 988 SPIs. The Distributor assigns each SPI an interrupt ID number, INTID[1019:32], and it distributes interrupts it receives on the **spi[x:0]** signals to any CPU Interface that the programming of the Target Register specifies.

# 2.2.3 Legacy interrupts

Depending on the GIC configuration, the Distributor can provide up to two legacy interrupt inputs, for each processor that connects to the GIC.

—— Note ———

- When the GIC is configured to support the Secure state only then you can configure the GIC to provide a legacy nirg c < n > for each CPU Interface that the GIC contains.

- When the GIC is configured to support the Security Extensions then you can configure the GIC to provide a legacy\_nfiq\_c<n> and legacy\_nirq\_c<n> for each CPU Interface that the GIC contains.

See the *ARM Generic Interrupt Controller Architecture Specification* for information about how to program the CPU Interface Control Register to route the legacy interrupt inputs to the interrupt outputs of a CPU Interface, that is, **nfiq\_c<n>** and **nirq\_c<n>**.

#### 2.2.4 Programmable trigger-mode of PPIs

The GIC does not permit use of the Interrupt Configuration Register to program the trigger mode of PPIs.

— Note —

- The interrupt configuration of a PPI is set during configuration and can be either:

- level-sensitive active HIGH

- pulse-sensitive.

- The AMBA Designer documentation provides information about configuring the triggering mechanism of PPIs, see *Additional reading* on page xii.

# 2.2.5 Lockable SPI (LSPI) support

The GIC supports a configurable number of LSPIs. The AMBA Designer documentation provides information about configuring the number of LSPIs you require, see *Additional reading* on page xii.

—— Note ———

The LSPI field in the Interrupt Controller Type Register defines which INTIDs are LSPIs. See *Interrupt Controller Type Register (ICDICTR)* on page 3-6.

### 2.2.6 Number of priority levels

The number of priority levels that the GIC supports is configurable. The AMBA Designer documentation provides information about configuring the GIC, see *Additional reading* on page xii.

#### 2.2.7 Effect of updating the Priority Level Register for Active interrupts

When you change the priority level of an interrupt that is either Active or Active-and-pending then the GIC immediately uses the new priority level for the Active interrupt.

#### 2.2.8 Interrupt prioritization of interrupts with equal priority

If two or more interrupts, with the same priority level, are the highest Pending interrupts then depending on the interrupt type the Distributor arbitrates as follows:

**PPI, SPI** The Distributor issues the interrupt with the lowest INTID.

**SGI** The Distributor issues the SGI with the lowest INTID. In multiprocessor systems, if a priority level conflict remains, the Distributor issues the SGI that was requested by the processor with the lowest CPUID. Therefore when a priority level conflict occurs, an SGI request from processor 0 has the highest priority and an SGI request from processor 7 has the lowest priority.

— Note ——

The Distributor excludes INTIDs from entering the prioritization logic if they are in the Active-and-pending state.

# 2.2.9 Arbitration of SPIs which target multiple processors

The GIC performs no arbitration when an SPI signals an interrupt to multiple processors. Under these circumstances, all the targeted processors are signaled the SPI at the same time and it is the first processor to respond by reading their Interrupt Acknowledge Register that receives the INTID of the SPI. The GIC ensures that all of the remaining processors that were targeted receive a spurious interrupt response.

# 2.2.10 Initial value of the Interrupt Security Register

The GIC resets all bits in the Interrupt Security Register to zero.

# 2.2.11 Access restrictions of registers that are specific to a CPU Interface

When a GIC contains multiple CPU Interfaces then the GIC permits a processor in:

- Secure state to access all the registers for any other CPU Interface

- Non-secure state to access registers for any other CPU Interface, but only those registers that permits non-secure accesses.

See enable and match signals on page 2-7 for more information.

# 2.2.12 Minimum supported value in the Binary Point Register

The minimum value in the Binary Point Register depends on the number of priority levels that the GIC is configured to support.

# Chapter 3 Programmers Model

This chapter describes the GIC registers and provides information for programming the device. It contains the following sections:

- *About the programmers model* on page 3-2

- Distributor register descriptions on page 3-5.

- CPU Interface register descriptions on page 3-30

- *Additional programming information* on page 3-33.

# 3.1 About the programmers model

The GIC provides the following register maps:

- Distributor register map

- *CPU Interface register map* on page 3-4.

The following information applies to the GIC registers:

- The base address of the GIC is not fixed, and can be different for any particular system implementation. The offset of each register from the base address is fixed.

- Do not attempt to access reserved or unused address locations. Attempting to access these location can result in Unpredictable behavior of the GIC.

- Unless otherwise stated in the accompanying text:

- do not modify undefined register bits

- ignore undefined register bits on reads

- all register bits are reset to a logic 0 by a system or power-on reset.

- Accesses can be byte, halfword, or word.

- The GIC only supports data in little-endian format.

- The Type column in Table 3-1 on page 3-5 and Table 3-18 on page 3-30 describes the access types as follows:

- **RW** Read and write.

- **RO** Read only.

- **WO** Write only.

## 3.1.1 Distributor register map

The register map of the Distributor spans a 4KB region, as Figure 3-1 on page 3-3 shows.

| ~                          |                         | t :d [2:0]                         |           |                    |  |  |  |

|----------------------------|-------------------------|------------------------------------|-----------|--------------------|--|--|--|

|                            | componen                | 0xFF0                              |           |                    |  |  |  |

| PrimeCell                  |                         | periph_id_[3:0]<br>periph_id_[7:4] |           |                    |  |  |  |

| configuration              | penpii_i                | u_[7.4]                            |           | 0xFD0              |  |  |  |

|                            | Reserved                | peri                               | ph_id_8   | 0xFC0              |  |  |  |

| SGI control 🤇              | sgi_co                  | ontrol                             |           | 0xF00              |  |  |  |

| $\bigcap$                  | enable                  | _d <n></n>                         |           |                    |  |  |  |

|                            | match                   | _d <n></n>                         |           | 0xDE4              |  |  |  |

| Integration test $\langle$ | Rese                    | rved                               |           | 0xDE0<br>0xDDC     |  |  |  |

|                            | Rese                    | rved                               |           | 0xDDC<br>0xDD8     |  |  |  |

|                            | legacy_                 | int <n></n>                        |           | 0xDD3<br>0xDD4     |  |  |  |

| _                          |                         |                                    |           | 0,004              |  |  |  |

| ppi_c <n> and</n>          | sp                      | bi                                 |           |                    |  |  |  |

| <b>spi</b> signal status   | <br>ppi_ii              |                                    |           | 0xD04-0xDª         |  |  |  |

|                            |                         |                                    |           | 0xD00              |  |  |  |

|                            | ani a                   | anfia                              |           |                    |  |  |  |

|                            | spi_c                   | 0xC00-0xC <sup>a</sup>             |           |                    |  |  |  |

|                            | targets spi             |                                    |           |                    |  |  |  |

|                            | taigets_spi             | 0x820-0x <sup>a</sup>              |           |                    |  |  |  |

|                            | priority_spi            |                                    |           |                    |  |  |  |

|                            | priority ppi_<          | 0x420-0xª                          |           |                    |  |  |  |

|                            | priority_sgi_<          | 0x410                              |           |                    |  |  |  |

|                            |                         | 0x400                              |           |                    |  |  |  |

|                            | spi_a                   | ctive                              |           | 0x304-0x3ª         |  |  |  |

| configuration              | ppi_active_if <n></n>   | sgi_active_if<                     | :n>       | 0x304-0x3<br>0x300 |  |  |  |

|                            |                         | 0x300                              |           |                    |  |  |  |

|                            | spi_pe                  | 0x204-0x2ª                         |           |                    |  |  |  |

|                            | ppi_pending_if <n></n>  | sgi_pending_i                      | í <n></n> | 0x204-0x2<br>0x200 |  |  |  |

|                            |                         |                                    |           | 0,200              |  |  |  |

|                            | spi_er                  | 0x104-0x1ª                         |           |                    |  |  |  |

|                            | ppi_enable_if <n></n>   |                                    | 0x100     |                    |  |  |  |

|                            |                         |                                    | 0/1200    |                    |  |  |  |

|                            | spi_se                  | 0x084-0x0ª                         |           |                    |  |  |  |

| Ĺ                          | ppi_security_if <n></n> | sgi_security_i                     | <n></n>   | 0x080              |  |  |  |

|                            | dist_i                  | dent                               |           | 0.000              |  |  |  |

| Distributor configuration  | ic_ty                   | vpe                                |           | 0x008              |  |  |  |

| configuration              | ena                     | -                                  |           | 0x004              |  |  |  |

| <u> </u>                   | -                       | 0x000                              |           |                    |  |  |  |

<sup>a</sup> The upper limit for this register depends on the configuration of the GIC

## Figure 3-1 Distributor register map

In Figure 3-1, the register map consists of the following regions:

#### **Distributor configuration**

Use these registers to determine the global configuration of the Distributor and control its operating state.

## **INTID** configuration

These registers provide the operating parameters for each INTID.

#### ppi\_c<n> and spi status

These registers return the present logic status of the **ppi\_c<n>** and **spi** inputs.

#### **Integration test**

Use these registers when testing the integration of the GIC in a *System-on-Chip* (SoC). See *Distributor integration test registers* on page 4-3 for more information.

SGI control Use this register to generate an SGI.

#### **PrimeCell configuration**

These registers enable the identification of system components by software.

See Distributor register descriptions on page 3-5 for information about the registers.

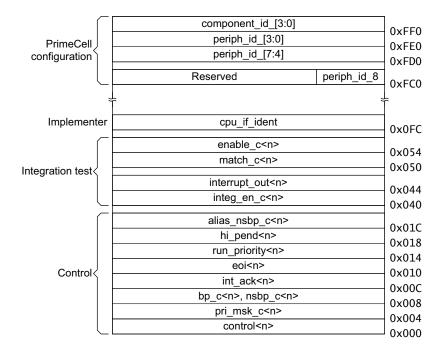

## 3.1.2 CPU Interface register map

The register map for each CPU Interface spans a 4KB region, as Figure 3-2 shows.

#### Figure 3-2 CPU Interface register map

In Figure 3-2, the register map consists of the following regions:

**Control** Use these registers to control the operating state of the CPU Interface.

#### **Integration test**

Use these registers to test the integration of the GIC in an SoC. See *CPU Interface integration test registers* on page 4-7 for more information.

#### Implementer

Identifies the implementer, and revision, of the CPU Interface.

#### **PrimeCell configuration**

These registers enable the identification of system components by software.

See CPU Interface register descriptions on page 3-30 for information about the registers.

# 3.2 Distributor register descriptions

This section describes the registers that the Distributor provides. Table 3-1 lists the Distributor registers and provides a reference to the register description, which is either in this book or the *ARM Generic Interrupt Controller Architecture Specification*.

| Offset      | Name                                     | Туре | Reset      | Width | Description                                                              |

|-------------|------------------------------------------|------|------------|-------|--------------------------------------------------------------------------|

| 0×000       | enable                                   | RW   | 0x00000000 | 32    | Distributor Control Register (ICDDCR) <sup>a</sup>                       |

| 0x004       | ic_type                                  | RO   | _b         | 32    | Interrupt Controller Type Register (ICDICTR) on page 3-6                 |

| 0x008       | dist_ident                               | RO   | 0x0043Bc   | 32    | Distributor Implementer Identification Register<br>(ICDIIDR) on page 3-8 |

| 0x00C-0x07C | -                                        | -    | -          | -     | Reserved                                                                 |

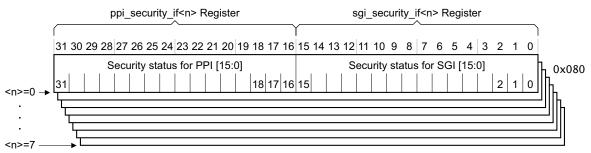

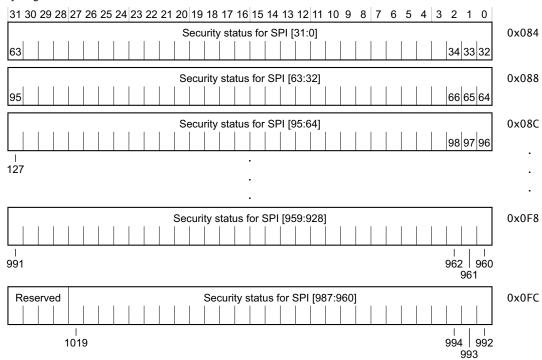

| 0x080       | sgi_security_if <n>d</n>                 |      | 0x0000     | 16    |                                                                          |

| 0x082       | ppi_security_if <n>d</n>                 | RW   | 0x0000     | 16    | Interrupt Security Registers (ICDISRn) on                                |

| 0x084-0x0FC | spi_security                             |      | 0x00000000 | 32    | page 3-8                                                                 |

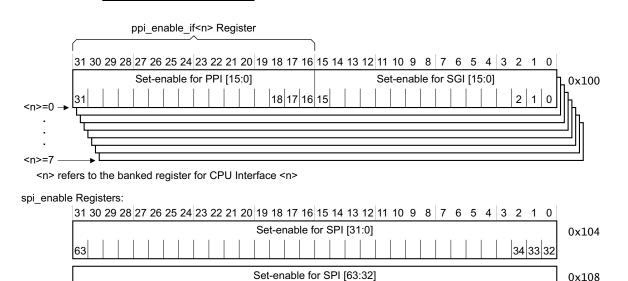

| 0x100       | -                                        | RO   | _b         | 16    |                                                                          |

| 0x102       | ppi_enable_if <n>d</n>                   | RW   | _b         | 16    | Enable Set Registers (ICDISERn) on page 3-9                              |

| 0x104-0x17C | spi_enable                               | RW   | 0x00000000 | 32    |                                                                          |

| 0x180       | -                                        | RO   | _b         | 16    |                                                                          |

| 0x182       | ppi_enable_if <n>d</n>                   | RW   | _b         | 16    | Enable Clear Registers (ICDICERn) on page 3-11                           |

| 0x184-0x1FC | spi_enable                               | RW   | 0x00000000 | 32    | page 5-11                                                                |

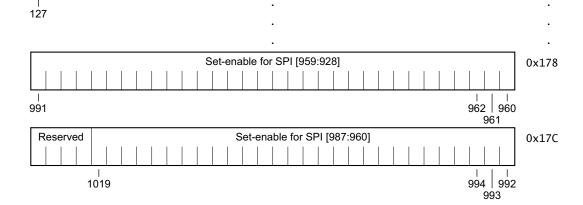

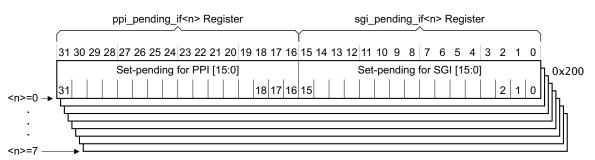

| 0x200       | sgi_pending_if <n>d</n>                  | RO   | 0x0000     | 16    |                                                                          |

| 0x202       | ppi_pending_if <n>d</n>                  | RW   | 0×0000     | 16    | Pending Set Registers (ICDISPRn) on page 3-12                            |

| 0x204-0x27C | spi_pending                              | RW   | 0x00000000 | 32    |                                                                          |

| 0x280       | sgi_pending_if <n>d</n>                  | RO   | 0x0000     | 16    |                                                                          |

| 0x282       | ppi_pending_if <n>d</n>                  | RW   | 0x0000     | 16    | Pending Clear Registers (ICDICPRn) on page 3-13                          |

| 0x284-0x2FC | spi_pending                              | RW   | 0x00000000 | 32    | p.60 5 15                                                                |

| 0x300       | sgi_active_if <n>d</n>                   |      | 0x0000     | 16    |                                                                          |

| 0x302       | ppi_active_if <n>d</n>                   | RO   | 0x0000     | 16    | Active Status Registers (ICDABRn) on page 3-15                           |

| 0x304-0x37C | spi_active                               |      | 0x00000000 | 32    |                                                                          |

| 0x380-0x3FC | -                                        | -    | -          | -     | Reserved                                                                 |

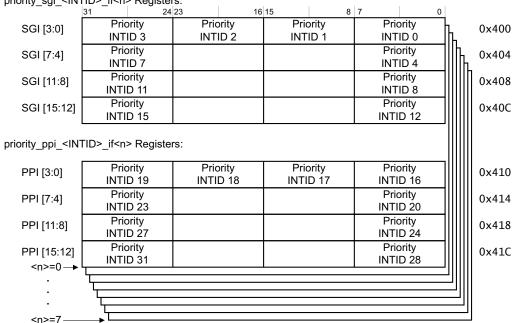

| 0x400-0x40F | priority_sgi_ <intid>_if<n>d</n></intid> |      |            |       |                                                                          |

| 0x410-0x41F | priority_ppi_ <intid>_if<n>d</n></intid> | RW   | 0x00       | 8     | Priority Level Registers (ICDIPRn) on page 3-10                          |

| 0x420-0x7FB | priority_spi_ <intid></intid>            |      |            |       |                                                                          |

| 0x7FC       | -                                        | -    | -          | 32    | Reserved                                                                 |

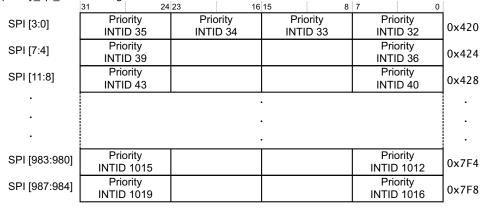

| 0x800-0x81F | -                                        | RO   | _b         | 0     | Taugat Dagistans (ICDIDTDa) on page 2,19                                 |

| 0x820-0xBFB | targets_spi_ <intid></intid>             | RW   | 0x00       | 8     | Target Registers (ICDIPTRn) on page 3-18                                 |

| ØxBFC       | -                                        | -    | -          | 32    | Reserved                                                                 |

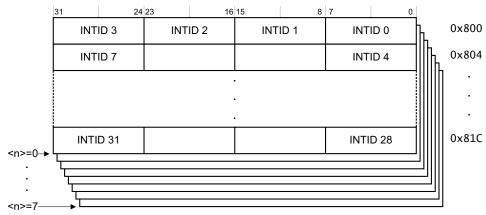

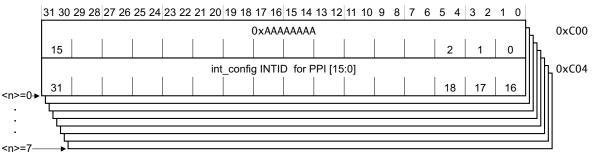

| 0xC00-0xC04 | -                                        | RO   | h          | 22    | Interrupt Configuration Registers (ICDICRn) on                           |

| 0xC08-0xCFC | spi_config                               | RW   | _b         | 32    | page 3-19                                                                |

## Table 3-1 Distributor register summary

| Offset                                 | Name                                                               | Туре            | Reset          | Width     | Description                                                  |

|----------------------------------------|--------------------------------------------------------------------|-----------------|----------------|-----------|--------------------------------------------------------------|

| 0xD00                                  | ppi_if <n>d</n>                                                    | RO <sup>e</sup> | 0×00000000     | 32        | PPI Status Register on page 3-20                             |

| 0xD04-0xD7C                            | spi                                                                | RO <sup>e</sup> | 0×00000000     | 32        | SPI Status Registers on page 3-21                            |

| 0xD80-0xDD0                            | -                                                                  | -               | -              | -         | Reserved                                                     |

| 0xDD4<br>0xDD8-0xDDC<br>0xDE0<br>0xDE4 | legacy_int <n>d<br/>-<br/>match_d<n>d<br/>enable_d<n>d</n></n></n> | See Ch          | apter 4 Progra | mmers Moo | del for Test for information about these registers.          |

| 0xDE8-0xEFC                            | -                                                                  | -               | -              | -         | Reserved                                                     |

| 0xF00                                  | sgi_control                                                        | WO              | -              | 32        | Software Generated Interrupt Register (ICDSGIR) <sup>a</sup> |

| 0xF04-0xFBC                            | -                                                                  | -               | -              | -         | Reserved                                                     |

| 0xFC0                                  | periph_id_8                                                        | RO              | _b             | 8         | Peripheral Identification Registers on page 3-22             |

| 0xFC4-0xFCC                            | -                                                                  | -               | -              | -         | Reserved                                                     |

| 0xFD0-0xFDC                            | periph_id_[7:4]<br>periph_id_[3:0]                                 | RO              | _b             | 8         | Peripheral Identification Registers on page 3-22             |

| 0xFE0-0xFEC                            | peripii_id_[5.0]                                                   |                 |                |           |                                                              |

#### Table 3-1 Distributor register summary (continued)

a. See the ARM Generic Interrupt Controller Architecture Specification.

b. The reset value depends on the configuration of the GIC.

c. The reset value depends on the revision of the GIC. See Distributor Implementer Identification Register (ICDIIDR) on page 3-8.

d. <n> corresponds to the number of a CPU Interface. If the GIC contains two or more CPU Interfaces then the **enable\_d<n>** and **match\_d<n>** signals control which banked register is selected.

e. Only processors in Secure state can access this Implementation-defined register.

## 3.2.1 Interrupt Controller Type Register (ICDICTR)

The ic\_type Register characteristics are:

| Purpose | Provides | information | about the | configuration | of the GIC. |

|---------|----------|-------------|-----------|---------------|-------------|

|         |          |             |           |               |             |

Usage constraints No usage constraints.

**Configurations** This register is available in all configurations of the GIC.

Attributes See the register summary in Table 3-1 on page 3-5.

Figure 3-3 shows the ic\_type Register bit assignments.

| 31 |   |     | 16 | 15   | 11  | 10 | 98  | 7 5           | 4                  | 0 |

|----|---|-----|----|------|-----|----|-----|---------------|--------------------|---|

|    | S | SBZ |    | LSPI |     |    | SBZ | CPU<br>number | IT lines<br>number |   |

|    |   |     |    |      | TZ- |    |     |               |                    |   |

## Figure 3-3 ic\_type Register bit assignments

Table 3-2 shows the ic\_type Register bit assignments.

#### Table 3-2 ic\_type Register bit assignments

| Bits    | Name            | Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [31:16] | -               | SBZ.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [15:11] | LSPI            | Returns the number of <i>Lockable Shared Peripheral Interrupts</i> (LSPIs) that the GIC contains:<br>b00000 = no LSPIs<br>b00001 = 1 LSPI. INTID32<br>b00010 = 2 LSPIs, INTID32 - INTID33<br>b00011 = 3 LSPIs, INTID32 - INTID34                                                                                                                                                                                       |

|         |                 |                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                 | b11110 = 30 LSPIs, INTID 32 - INTID 61                                                                                                                                                                                                                                                                                                                                                                                 |

|         |                 | b11111 = 31 LSPIs, INTID32 - INTID62.                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                 | When <b>cfgsdisable</b> is HIGH then the GIC prevents writes to any register locations that control the operating state of an LSPI that is programmed to be secure. See the <i>ARM Generic Interrupt Controller Architecture Specification</i> for more information about <b>cfgsdisable</b> .                                                                                                                         |

|         |                 | Note                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |                 | The AMBA Designer documentation provides information about configuring the number of LSPIs you require, see <i>Additional reading</i> on page xii.                                                                                                                                                                                                                                                                     |

| [10]    | TZ              | Returns the number of security states that the GIC supports:                                                                                                                                                                                                                                                                                                                                                           |

|         |                 | 0 = the GIC supports the Secure state                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                 | 1 = the GIC supports a Secure state and a Non-secure state.                                                                                                                                                                                                                                                                                                                                                            |

| [9:8]   | -               | SBZ.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| [7:5]   | CPU number      | Returns the number of CPU Interfaces that the GIC provides. The GIC provides either:<br>b000 = one CPU Interface<br>b001 = two CPU Interfaces<br>b010 = three CPU Interfaces<br>b011 = four CPU Interfaces<br>b100 = five CPU Interfaces<br>b101 = six CPU Interfaces<br>b110 = seven CPU Interfaces<br>b111 = eight CPU Interfaces.                                                                                   |

| [4:0]   | IT lines number | Returns the number of INTIDs, to the nearest 32, that the Distributor provides:<br>b00000 = the Distributor provides 1-32 INTIDs <sup>a</sup><br>b00001 = the Distributor provides 33-64 INTIDs<br>b00010 = the Distributor provides 65-96 INTIDs<br>b00011 = the Distributor provides 97-128 INTIDs<br>b11110 = the Distributor provides 961-992 INTIDs<br>b11111 = the Distributor provides 993-1020 INTIDs.<br>Mote |

a. The Distributor always uses INTID0 to INTID31, to control any SGIs and PPIs that a configured GIC contains.

## 3.2.2 Distributor Implementer Identification Register (ICDIIDR)

The dist\_ident Register characteristics are:

| Purpose                                                  | Provides information about the implementer of the Distributor and the revision of the GIC. |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Usage constraints                                        | No usage constraints.                                                                      |  |  |

| Configurations                                           | This register is available in all configurations of the GIC.                               |  |  |

| Attributes                                               | See the register summary in Table 3-1 on page 3-5.                                         |  |  |

| Figure 3-4 shows the dist_ident Register bit assignments |                                                                                            |  |  |

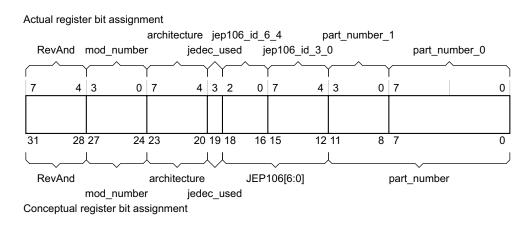

Figure 3-4 shows the dist\_ident Register bit assignments.

| 31 24    | 23 12   | 11 0        |