Unité: Systèmes séquentiels avancés (SSA)

# Interface : bus et mémoires

heig-vd

Haute Ecole d'Ingénierie et de Gestion du Canton de Vaud

Etienne Messerli Institut REDS, HEIG-VD

30 avril 2013

Copyright ©2013 EMI, REDS@HEIG-VD

Interfaces & mémoires, p1

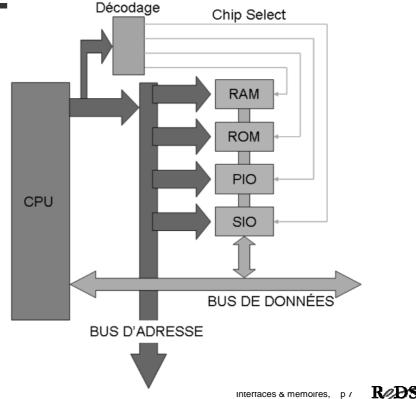

#### Plan d'adressage

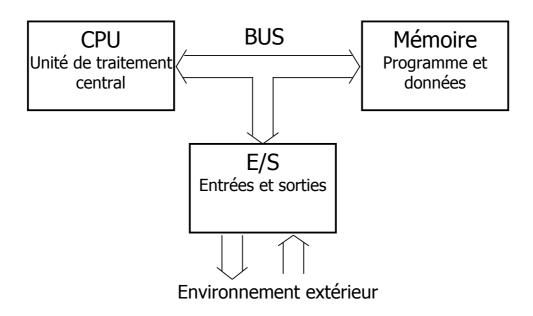

Bus commun à l'ensemble du système à processeur

#### Bus d'un système à processeur

#### Composé de trois parties:

- Bus d'adresse

- ✓ Générée par le maître du bus: le CPU

- ✓ Définit l'adresse concernée, le correspondant

- Bus de données

- ✓ Contient les données échangées entre le maître et le correspondant adressé

- Bus de contrôle

- ✓ Définit le sens du transfert, le protocole, ...

Copyright ©2013 EMI, REDS@HEIG-VD

Interfaces & mémoires, p 3

#### Bus d'adresses (address bus)

- L'adresse décrit

- ✓ position mémoire (ou I/O) d'un opérande

- ✓ position mémoire du code de la prochaine instruction à exécuter

- L'adresse est générée par le CPU

- Bus d'adresse: unidirectionnel

- Fréquent: memory address register (MAR)

- ✓ maintien de l'adresse sur le bus

#### Bus de données (data bus)

- Transmet:

- ✓ code des instructions de la mémoire vers le CPU

- ✓ opérandes entre le CPU et la mémoire ou les I/O (dans les 2 sens)

- Bus bidirectionnel de 4, 8, 16, 32 ou 64 bits

- Limitation en largeur: plusieurs transferts éventuellement nécessaires pour une information plus large que la taille du bus

- ✓ code d'une instruction (IR: plusieurs tranches)

- √ donnée sur plusieurs mots mémoire

Copyright ©2013 EMI, REDS@HEIG-VD

Interfaces & mémoires, p 5 Reps

#### Bus de commande

- Signaux de gestion des transferts

- ✓ sens, synchronisation, handshake, ...

- Exemples pour bus synchrones:

- ✓ RD: lecture (le CPU lit)

- √WR: écriture (le CPU écrit)

- ou alors

- √R/W pour le sens du transfert

- ✓ strobe pour la synchronisation

## Plan d'adressage mémoire et I/O

Copyright ©2013 EMI, REDS@HEIG-VD

R/DS

### Système MUO

Voir manuel "SysMU0":

• 1-1 Spécification du système à processeur MU0

### Les types de mémoires

- Les mémoires "vives"

- ✓ informations perdues à la mise hors tension

- ✓ lecture et écriture en cours d'utilisation

- Les mémoires "mortes"

- ✓ informations conservées à la mise hors tension

- ✓ lecture en cours d'utilisation

- ✓ écriture (« programmation ») durant la fabrication de la mémoire ou écriture particulière dans le système qui la contient

Copyright ©2013 EMI, REDS@HEIG-VD

Interfaces & mémoires. p 9

### Les types de mémoires

- ✓ RAM (random-access memory): mémoire vive, volatile

- → statique (SRAM): l'information est conservée tant que la tension d'alimentation est présente

- →dynamique (DRAM): il faut recharger (rafraîchir) périodiquement les cellules de mémoire pour conserver les données

- ✓ ROM† (read-only memory): contenu définit lors de la fabrication

- ✓ PROM† (programmable read-only memory): contenu programmable une seule fois

- ✓ EPROM (erasable programmable read-only memory): le contenu peut être effacé et modifié plusieurs fois

- → EEPROM (*electrically EPROM*) ou E2PROM: le contenu est effacé électriquement (quelques millisecondes)

- → Flash: le contenu est effacé et programmé électriquement plus rapidement que sur les EEPROM

#### Les mémoires vives

- SRAM Static RAM

- DRAM Dynamic RAM

- SDRAM Synchronous Dynamic RAM

- DDRAM Double-Data-rate SDRAM

Copyright ©2013 EMI, REDS@HEIG-VD

Interfaces & mémoires, p 11

#### RAMs dynamiques

Grandes capacités

2-8 Gb

Rapides

500MHz

- ✓ Attention latence

- Limitations accès (pages)

- Rafraichissement

- DRAMs asynchrones

- SDRAMs synchrones

#### Mémoires Flash

NAND

32Gb

- ✓ Haute capacité

- ✓ Contraintes: accès, correction erreur, ...

- ✓ Rapide en effacement et écriture

NOR

512Mb

- √ Accès aléatoire rapide

- ✓ Plus lente en effacement et écriture

- ✓ Plus chère

Copyright ©2013 EMI, REDS@HEIG-VD

Interfaces & mémoires, p 13

#### Mémoires EEPROM

Petites capacités

1Mb

- Sauvegarde de paramètres

- Parallèle ou série

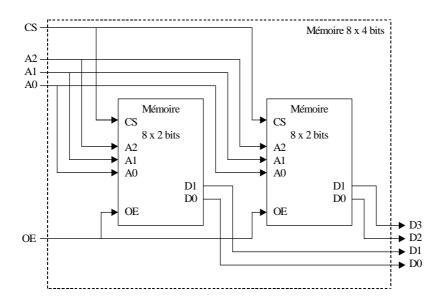

### Extension des données (largeur)

• Il suffit d'utiliser 2 circuits en parallèle

Copyright ©2013 EMI, REDS@HEIG-VD

Interfaces & mémoires, p 15

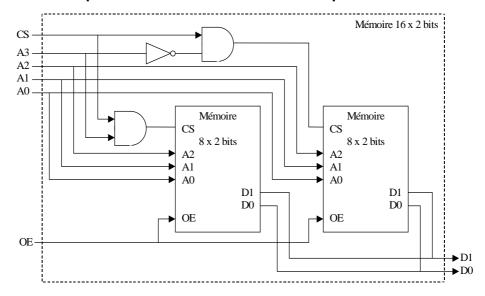

#### Extension des adresses (profondeur)

Les entrées de sélection du circuit permettent d'étendre la profondeur en utilisant plusieurs circuits