# Architecture des systèmes à processeur

Prof. Géraldine Conti

Basé sur les cours des Profs. Sanchez, Starkier, Mosqueron et Dassatti

1

Le processeur embarqué (Partie 2) – Les mémoires

|                   |      | Puissance de 2  |            |     |   |

|-------------------|------|-----------------|------------|-----|---|

|                   |      | r uissance de 2 |            |     |   |

|                   |      | 0               | 1          |     |   |

| 5                 |      | 1               | 2          |     |   |

| Puissances de 2   |      | 2               | 4          |     |   |

| i dissuffees de Z |      | 3               | 8          |     |   |

|                   |      | 4               | 16         |     |   |

|                   |      | 5               | 32         |     |   |

|                   |      | 6               | 64         |     |   |

|                   |      | 7               | 128        |     |   |

|                   |      | 8               | 256        |     |   |

|                   |      | 9               | 512        |     |   |

|                   | Kilo | 10              | 1024       | 1KB |   |

|                   |      | 11              | 2048       |     |   |

|                   |      | 12              | 4096       |     |   |

|                   |      | 13              | 8192       |     |   |

|                   |      | 14              | 16384      |     |   |

|                   |      | 15              | 32768      |     |   |

|                   |      | 16              | 65536      |     |   |

|                   |      | 17              | 131072     |     |   |

|                   |      | 18              | 262144     |     |   |

|                   |      | 19              | 524288     |     |   |

|                   | Mega | 20              | 1048576    | 1MB |   |

|                   |      | 21              | 2097152    |     |   |

|                   |      | 22              | 4194304    |     |   |

|                   |      | 23              | 8388608    |     |   |

|                   |      | 24              | 16777216   |     |   |

|                   |      | 25              | 33554432   |     |   |

|                   |      | 26              | 67108864   |     |   |

|                   |      | 27              | 134217728  |     |   |

|                   |      | 28              | 268435456  |     | 6 |

|                   |      | 29              | 536870912  |     | U |

|                   | Giga | 30              | 1073741824 | 1GB |   |

## Adresse de fin de mémoire à partir de 0x0000

|   | Adresse début | Adresse fin | Taille hexa | Taille Bytes | Taille bits |

|---|---------------|-------------|-------------|--------------|-------------|

| Α | 0x 0          | 0x          | 0x          | 1 KB         |             |

Quelle est l'adresse de fin (en hexadécimal) ?

## Adresse de fin de mémoire à partir d'une adresse donnée

|   | Adresse début | Adresse fin | Taille hexa | Taille bytes | Taille bits |

|---|---------------|-------------|-------------|--------------|-------------|

| Ε | 0x 40800200   | 0x          | 0x          | 12 MB        |             |

Quelle est l'adresse de fin (en hexadécimal)?

.

## La mémoire cache

#### Introduction

CPU à 2.6 GHz, mémoire RAM avec 10ns de latence. Le CPU veut accéder à une information mémoire.

- Après combien de temps va-t-il recevoir l'information ?

- Combien de cycles CPU se sont déroulés pendant ce temps ?

12

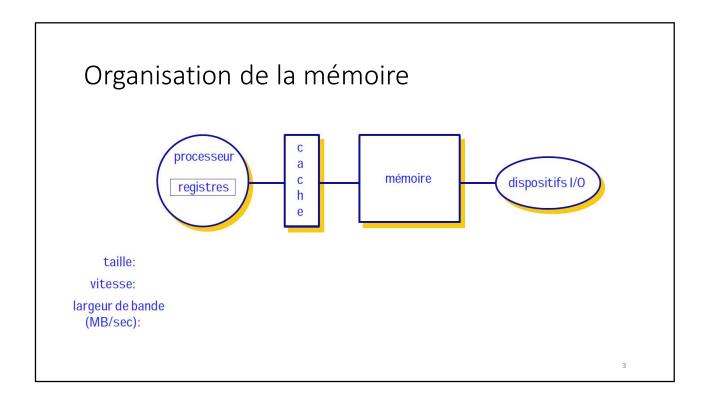

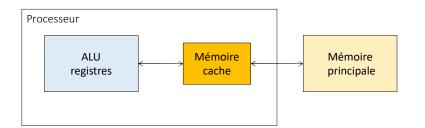

#### Généralités

- Aussi appelée antémémoire

- **Utilité** : zone de mémoire plus rapide que la RAM où on stocke une copie d'informations qui se trouvent en mémoire RAM

- La mémoire cache est composée de transistors, et non de condensateurs

- Même fréquence que le CPU

- Latence de quelques cycles CPU

- Aucun contrôle sur le contenu du cache : se remplit au fur et à mesure de l'exécution des programmes

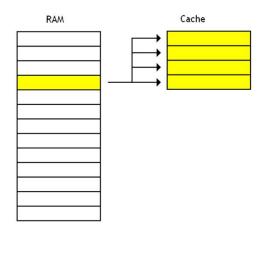

## Philosophie

• A la base du principe des caches

| Localité spatiale                                                                               | Localité temporelle                                                                                                                    |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Le code d'un programme s'exécute toujours à<br>l'intérieur de petites zones répétées de mémoire | Les blocs s'exécutent en séquences très proches                                                                                        |

| (des blocs correspondant à des boucles ou/et des sous-programmes).                              | il y a plus de chances d'accéder à une position de<br>mémoire utilisée il y a 10 cycles qu'à une autre<br>utilisée il y a 10000 cycles |

| Si une adresse mémoire est utilisée, alors les                                                  |                                                                                                                                        |

| adresses proches le seront probablement dans un futur proche.                                   | Si une adresse mémoire est utilisée, elle le sera<br>probablement à <b>nouveau</b> dans un futur proche                                |

1.5

## Principe général

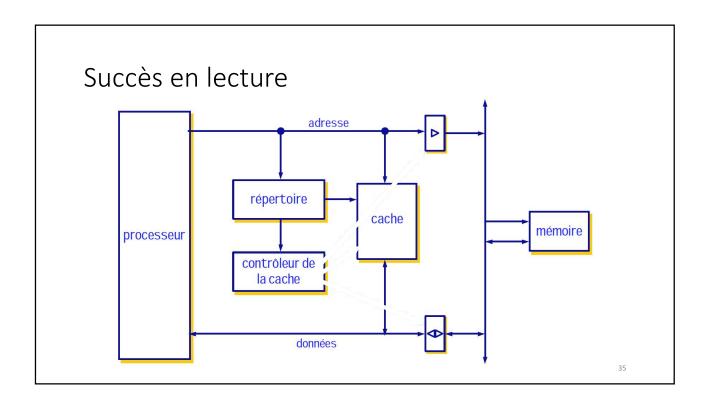

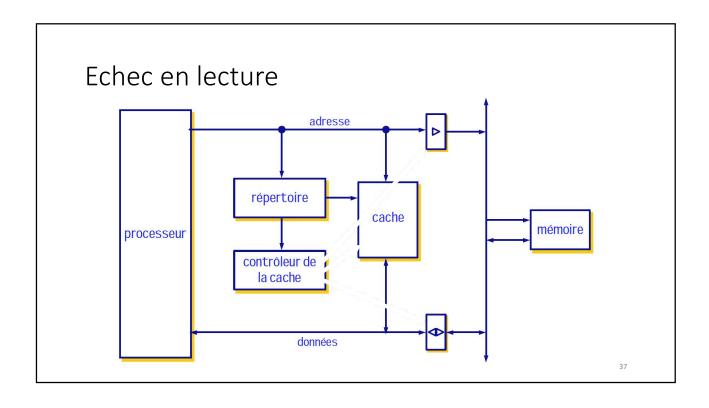

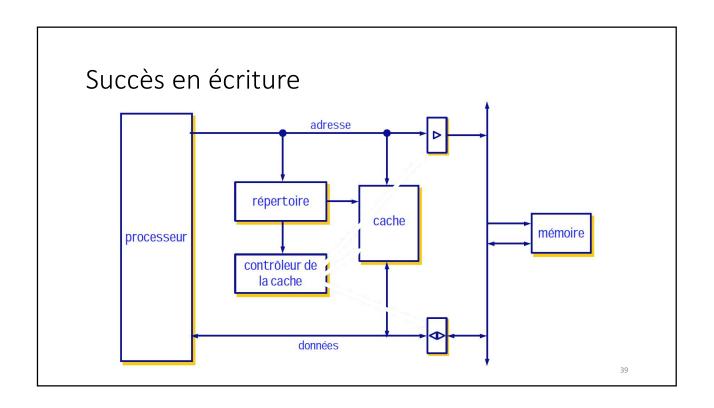

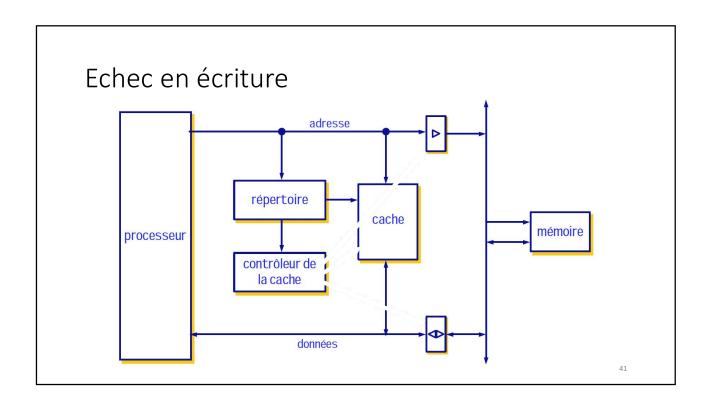

Le processeur essaie d'accéder un mot (octet) d'abord dans la cache

Succès (Hit):

La mémoire principale

n'est pas accédée

Echec (Miss): Le mot est gardé dans la cache pour un accès futur

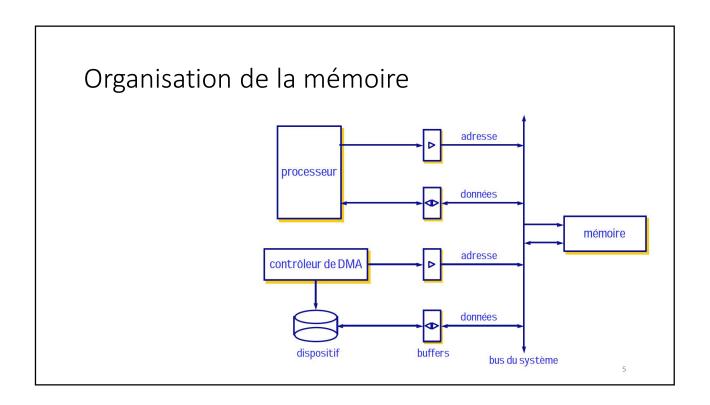

- Pour réduire le temps de mise à jour lors d'un échec, le **bus** entre mémoire et cache est plus large que celui entre cache et processeur.

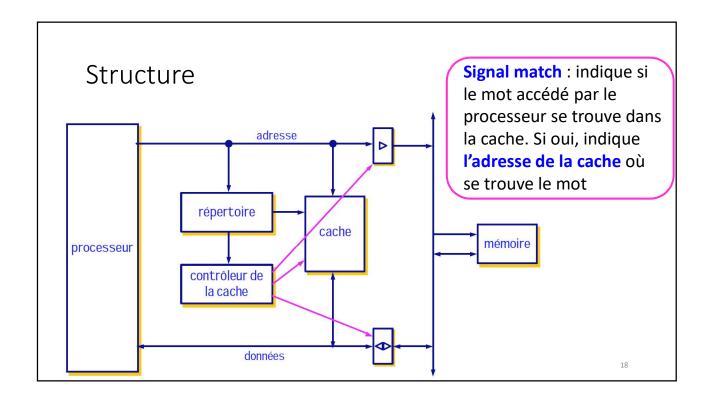

#### Structure interne

Ligne de cache

Tag

- Le cache est divisé en blocs/lignes

- Le bloc/ligne est un groupe d'octets (8-64)

- Combien de lignes dans un cache de 64Ko avec des lignes de 64 octets ?

- Pour les lignes de 64 octets, les octets d'adresse 0-63 seront dans la même ligne, ceux de 64-127 dans une autres,...

- Le bloc/ligne a une étiquette unique (tag)

- Les transferts entre cache et mémoire principale se font par lignes

19

#### Recherche dans la cache

- Trouver quelle est la ligne de cache dont le tag correspond à l'adresse de base demandée au répertoire

- 3 stratégies (cablées, non logicielles) :

- 1) Fully Associative

- 2) Direct Mapped

- 3) Set Associative

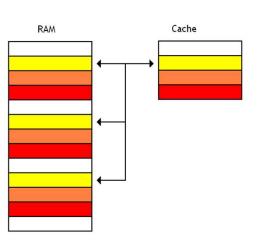

## **Fully Associative**

- un mot de la mémoire principale peut être stocké n'importe où dans la cache

- Avantages:

- Désavantages :

2

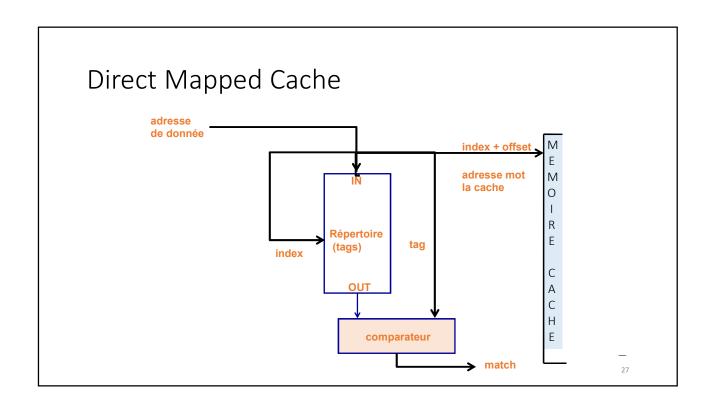

## Direct Mapped cache

- un mot de la mémoire principale est chargé dans une ligne de cache prédéfinie (toujours la même)

- Avantages:

- Désavantages :

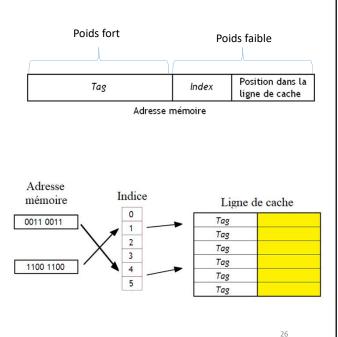

### Direct Mapped Cache

- L'adresse physique (32 bits) est divisée en deux parties :

- Bits de poids faible permettent de spécifier un index, qui indique à quelle ligne de la cache l'information se trouve, ainsi que la position dans la ligne

- Bits de poids fort forment un tag, qui est a comparer avec la valeur stockée dans le répertoire

- Bit de validité inclus

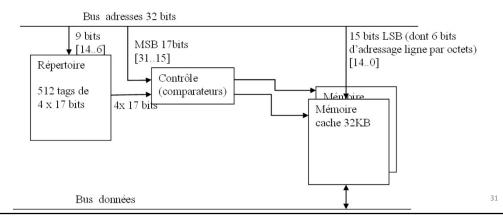

## Cache associative par voie

- Compromis

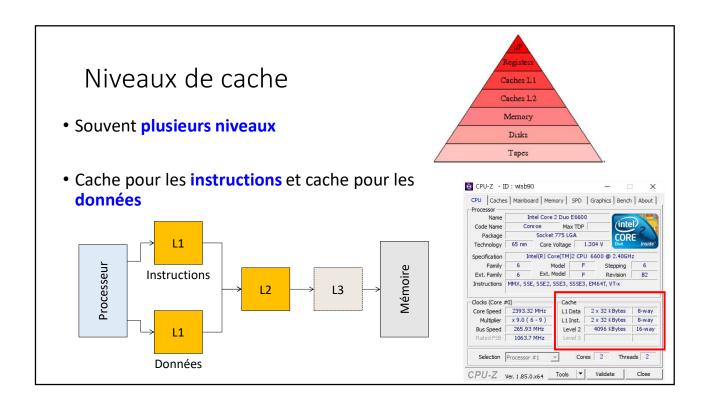

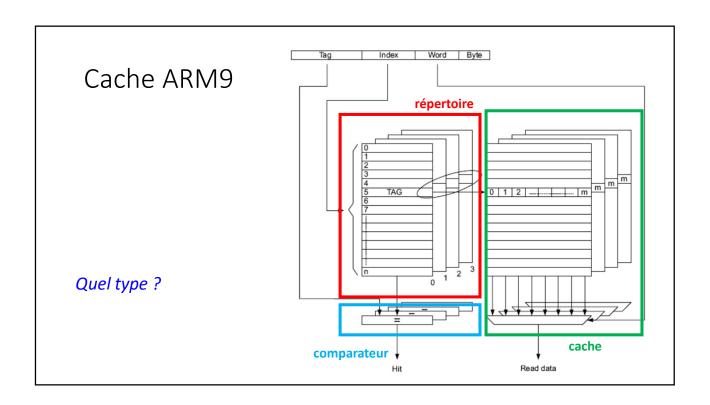

#### Cache ARM9: niveau L1

• 128KB: 4 voies associative de 32KB

• taille de ligne : 64 octets

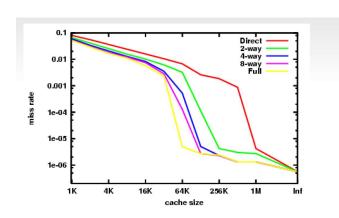

## Fréquence de succès

dépend de la taille de la cache et des politiques de placement

- Miss penalty >> Hit time

|            | Rate                                     | Time                                                                             |

|------------|------------------------------------------|----------------------------------------------------------------------------------|

| Cache Hit  | Nombre de hits/Nombre d'accès (Hit rate) | Temps d'accès à la cache (hit time)                                              |

| Cache Miss | 1 – (Hit rate)                           | Temps d'accès à la mémoire principale + temps de chargement cache (miss penalty) |

#### Exercice : fréquence de succès

- Si les accès à la mémoire demandent 3 wait states et la fréquence de succès est de 90% :

- La chute de la fréquence de succès à 80% fait doubler cette valeur

- Si une instruction demande 2 cycles sans wait state et 5 cycles avec, et si la fréquence de succès est de 80%, l'exécution de 10 instructions demande:

\_\_\_\_ cycles dont \_\_\_\_ sont faits avec la cache.

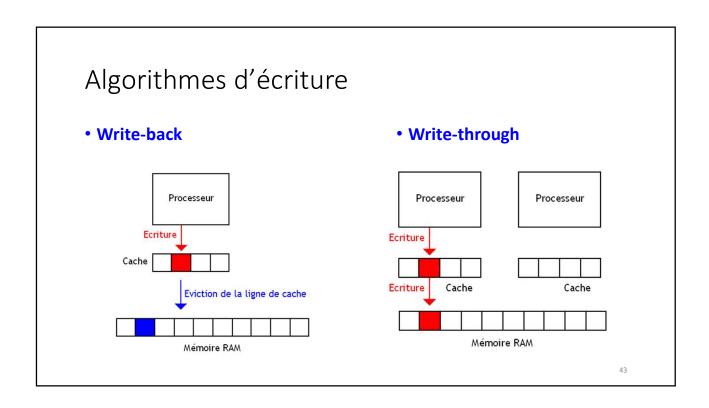

### Algorithmes d'effacement (cache miss)

- Il faut ajouter l'information manquante à la cache

- Si la cache est pleine, comment choisir la ligne à remplacer ?

|       | Fully associative | Direct Mapped | Set associative |

|-------|-------------------|---------------|-----------------|

| Choix |                   |               |                 |

• Politiques de remplacement

44

#### Exercice

Le bus d'adresse et le bus de donnée du processeur sont des bus 32 bits. On connecte au processeur une mémoire cache associative par ensemble de taille 64 kB. La taille d'une ligne est de 32 octets.

• Dessinez le schéma bloc de la mémoire cache et du répertoire associé en indiquant la taille des bus. Quelle est la taille du répertoire (nombre de tags) ?

La mémoire virtuelle

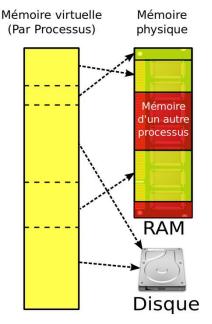

#### Mémoire virtuelle

- Fonctionnalité qui traduit des adresses virtuelles vues du logiciel en adresses physiques de mémoire vive

- Utilisations:

- compenser un manque de mémoire physique en transférant temporairement des données vers un stockage sur disque

- Mécanisme de protection de la mémoire

- Partager la mémoire entre processus

- Augmenter le taux de multiprogrammation

50

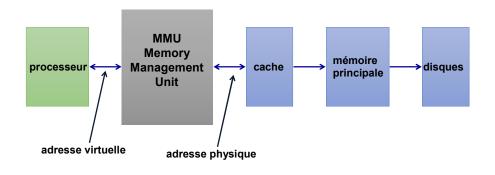

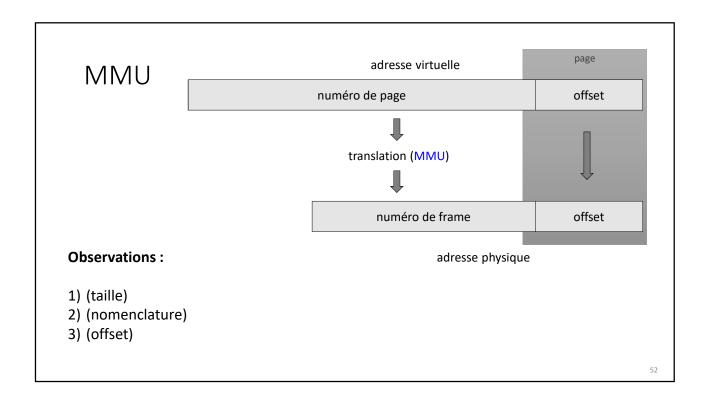

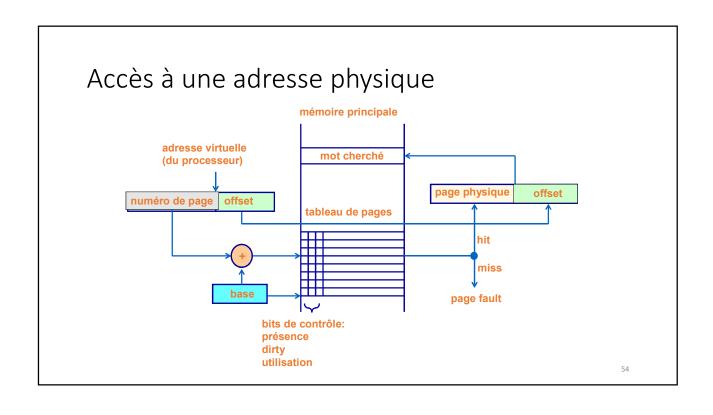

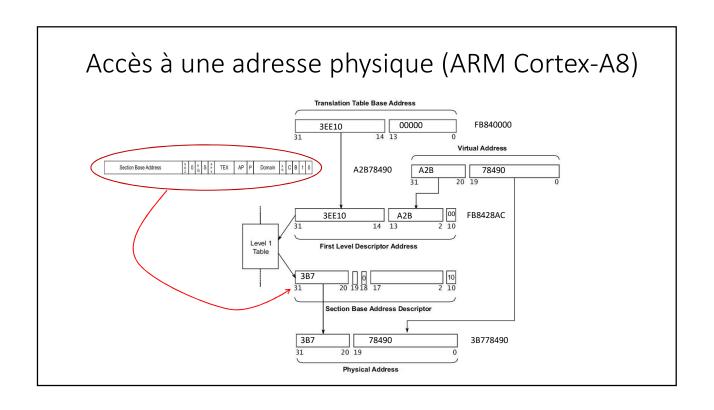

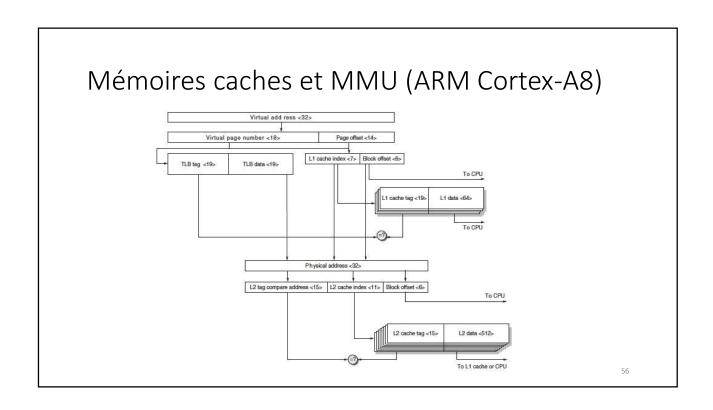

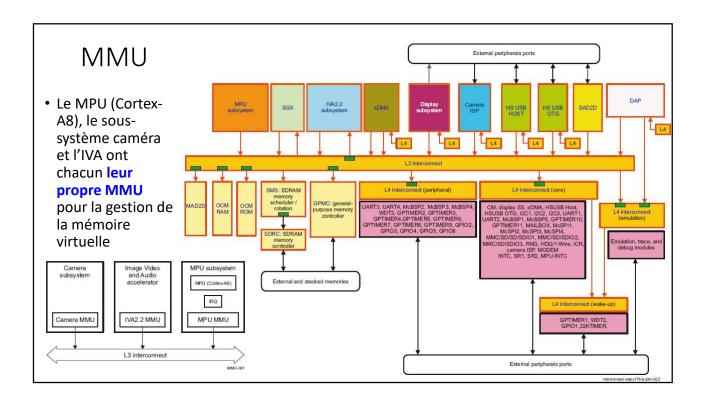

#### Memory Management Unit (MMU)

• Le transfert (permutation) est effectué par le MMU

#### Exercice 1

- La taille de page est 8K octets

- La taille de la mémoire virtuelle est 8 Go

- La taille de la mémoire physique est 256 Mo

Donnez le nombre de bits du numéro de page, du numéro de frame, et de l'offset

#### Réponse:

#### Exercice 2

Un processeur dispose d'une mémoire virtuelle constituée de 2 M pages de 256KB.

- Sachant que la mémoire physique peut contenir 2048 frames, donnez la taille de la mémoire virtuelle et celle de la mémoire physique.

- Le tableau des pages débute à l'adresse 0x1B800000 et contient des mots de 32bits. Si l'adresse virtuelle est 0x423CA34628, donnez l'adresse de l'entrée (mot) dans le tableau des pages qui contient le numéro de page physique.

60

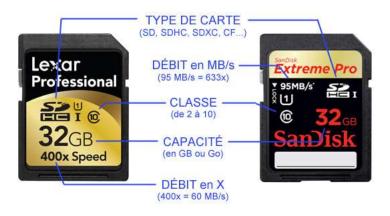

## Les cartes mémoire

63

#### DING YOUR MEMORY CAR

SD cards and Compact Flash memory cards carry a bewildering array of names, numbers and icons. Let us explain what they mean, and why they are important

- 1 'Extreme Pro' is just one of SanDisk's brand names It's not a defined standard for card performance. Most makers break up their memory cards into families

- **2** This logo tells you whether it's an SDHC card (which this one is), ordinary SD (rare these days) or SDXC.

- 3 If you see an additional 'There, it means the card conforms to the faster UHS-I standard. There's an even faster UHS-II standard found on the most expensive

- 4 This indicates the card capacity, Card capacity and speed don't always go together, though the more expensive cards generally offer both.

- 5 A number in a circle tells you the card's minimum speed

- video. Class 6 and Class 4 cards can do it in theory but may stutter or drop frames.

- 6 This 'I in a bucket' symbol indicates that this card also conforms to the UHS-I standard. It's broadly equivalent to Class 10 speed, but uses an intrinsically faster

- achieve this under ideal conditions. It's helpful for choosing a card for stills, but not for video, where you need a reliable minimum speed

- 8 This lock switch is unique to SD/SDHC/SDXC cards— you don't get it on Compact Flash cards. You can use to prevent accidental deletion of the card contents.

SD = Secure Digital

SDHC = High Capacity (max 32GB 2006)

SDXC = Extended Capacity (max 2TB 2011)

#### Taille:

SD 32 x 24 x 2.1/1.4 mm miniSD 21.5 x 20 x 1.4 mm microSD 11 x 15 x 1 mm

+ Multimedia Card

(MMC)

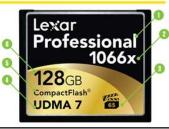

1 The 'Professional' branding identifies this memory card within the Lexar range, but it doesn't relate to any overall standard for Compact Flash memory cards.

- 2 The maximum speed of the memory card is sometimes quoted as a multiple of the old CD-ROM standard, which was 150KB/s. This card's '1066x' speed equates to 155MB/s.

- 3 Compact Flash cards don't use SD card 'Class' ratings for minimum sustained speed, but some have a VGP (Video Performance Guarantee) logo. VPG 20 is 20MB/s, VPG 65 is 65MB/s.

- 4 Newer memory cards use the faster UDMA standard, and all recent Nikon D-SLRs support UDMA (see the table overleaf), UDMA 7 is the newest and fastest variant.

- 5 Compact Flash cards once came in Type I and thicker Type II variants. Type II is no longer made and not supported by today's D-SLRs. All Compact Flash cards now are Type I.

- 6 Card capacity is quoted in GB, as it is with SD cards. This one has a capacity of 1286b, but Lexar has recently announced it is making a 256GB Compact Flash card.

66

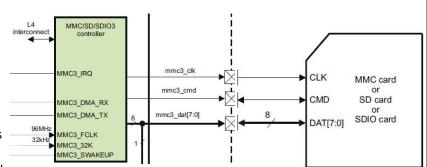

#### Protocole de communication

- Basé sur des échanges de messages:

- Command: initie une opération, envoyée en série sur la ligne mmci\_cmd.

- Response: envoyée en retour d'une commande en série sur la ligne mmci\_cmd

- Data: données transférées par les lignes data

- Busy: mmci\_dat0 signal maintenu à l'état bas

- CRC status: résultat envoyé par mmci\_dat0

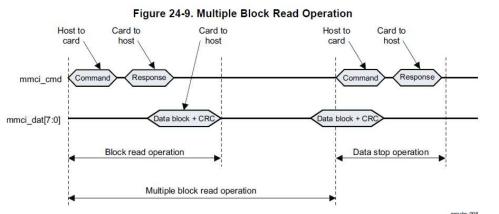

#### Lecture de données (DM3730)

- Se fait par blocs

- Transfert contrôlé par le host avec un «data stop» pour terminer le transfert

67

#### Ecriture de données (DM3730)

Ecriture contrôlée par le host avec lecture de «busy» et avec un «data stop» pour terminer le transfert

Figure 24-10. Multiple Block Write Operation with Card Busy Signal

Host to Card to Host to Card to host

mmci\_cmd

Command

Response

Data block

CRC

Setting

Busy

Data block

CRC

Setting

Busy

Data block

CRC

Setting

Data block

dates labos Rendus labos (minuit) Plan du cours 19.02 Introduction Révisions + architecture 26.02 Architecture Périphériques 05.03 Architecture (cache) Périphériques 4 12.03 Périphériques 5 Corrigé test, labo Périphériques 19.03 Parallélisme Périphériques 6 26.03 Périphériques 02.04 Parallélisme 8 Famille processeurs Sdcard Périphérique 09.04 16.04 Sdcard Corrigé test, labo Sdcard 10 30.04 4 laboratoires 11 07.05 Mémoires Sdcard 14.05 Bus Sdcard 12 Sdcard 21.05 13 Bus 28.05 **TEST** 14 04.06 Corrigé test, labo Picomon Sdcard 11.06 Labo Picomon Picomon Picomon